第二周主存储器组织

第1讲 存储器基本概念

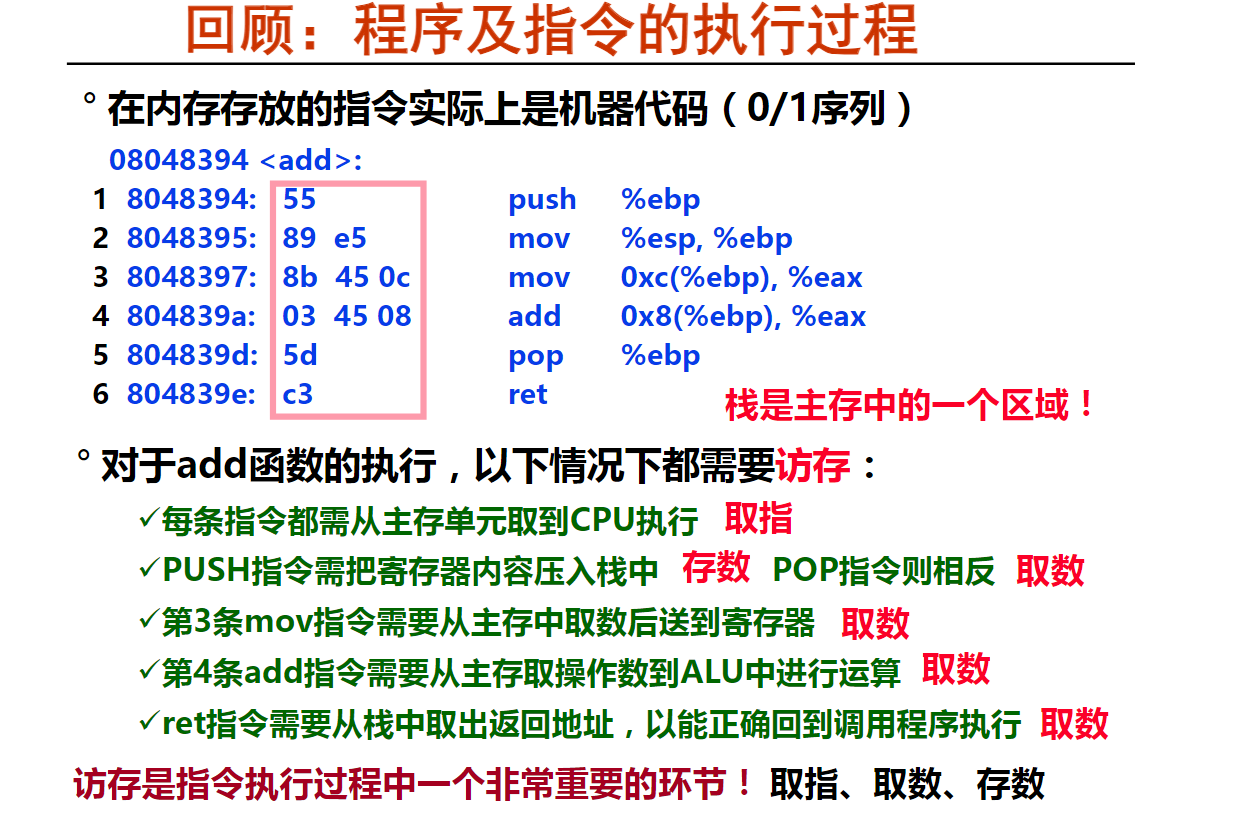

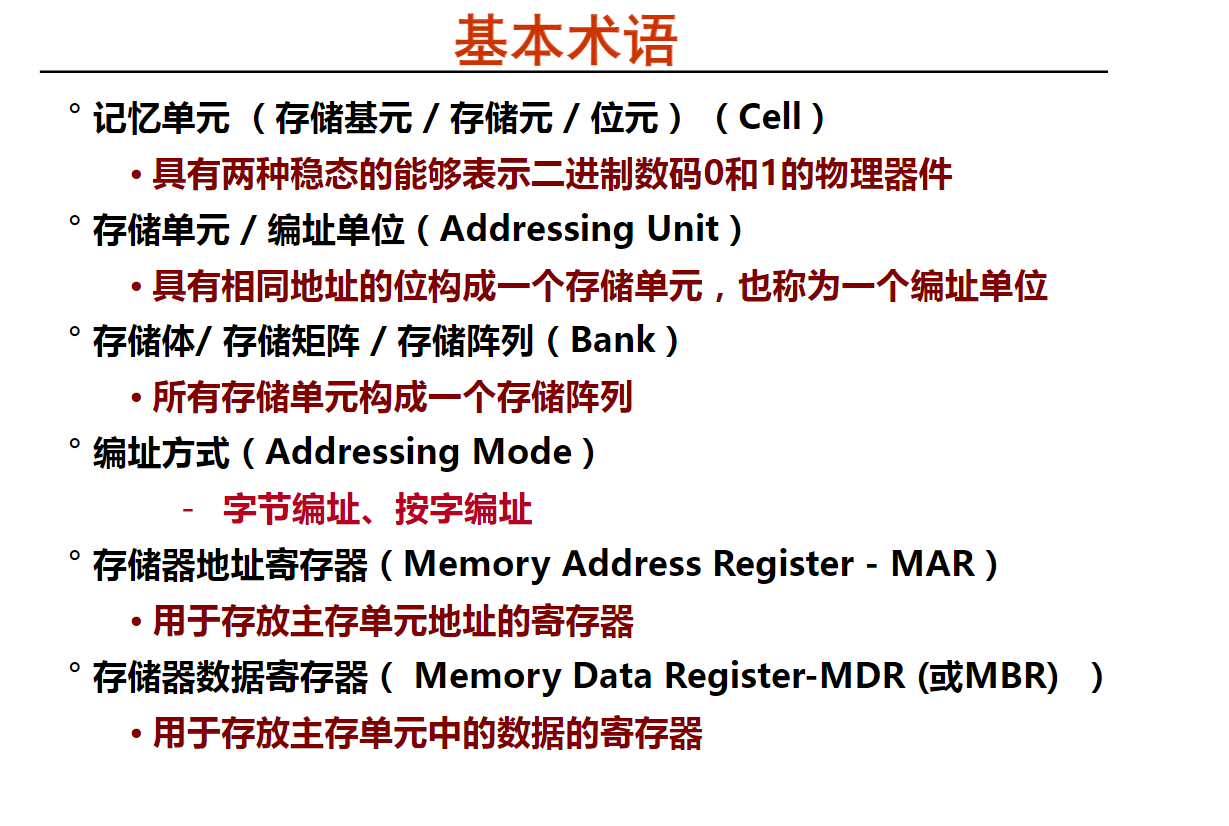

访存操作和基本术语

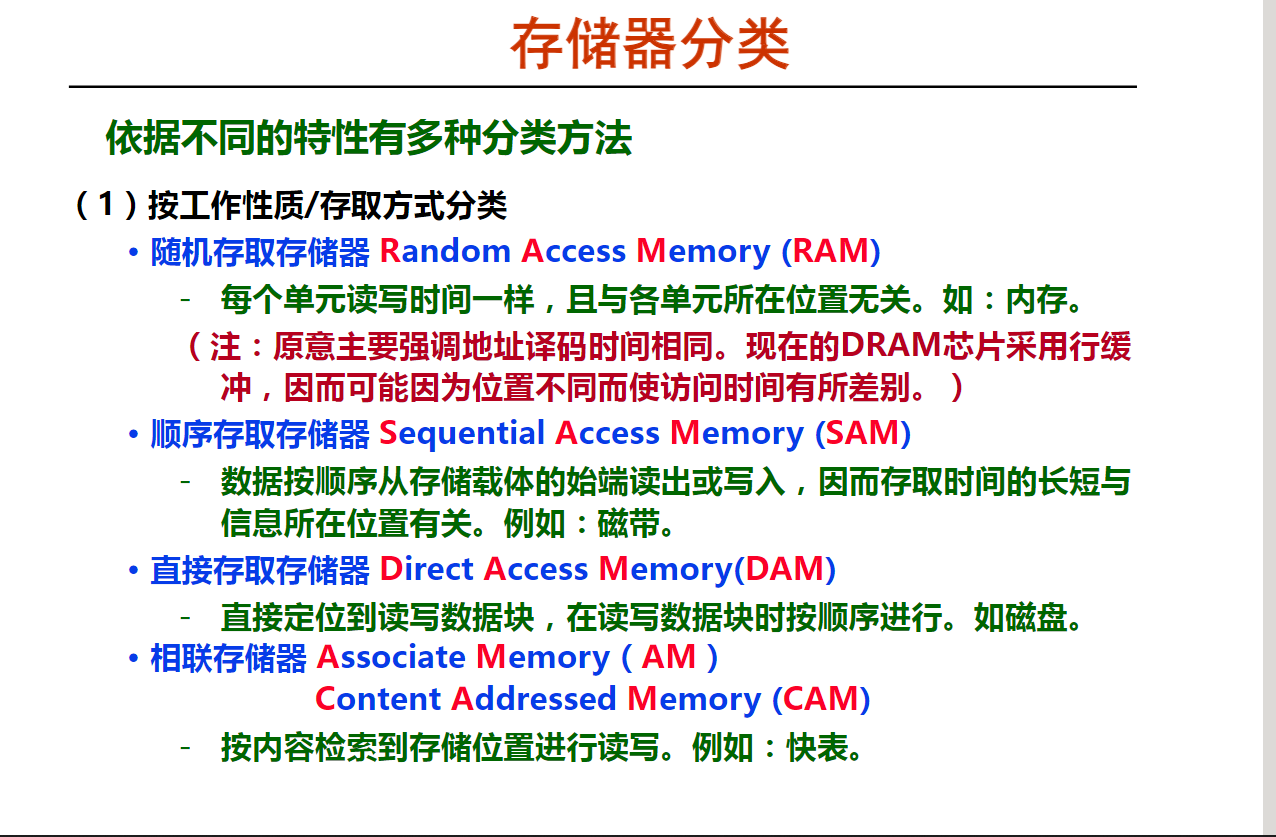

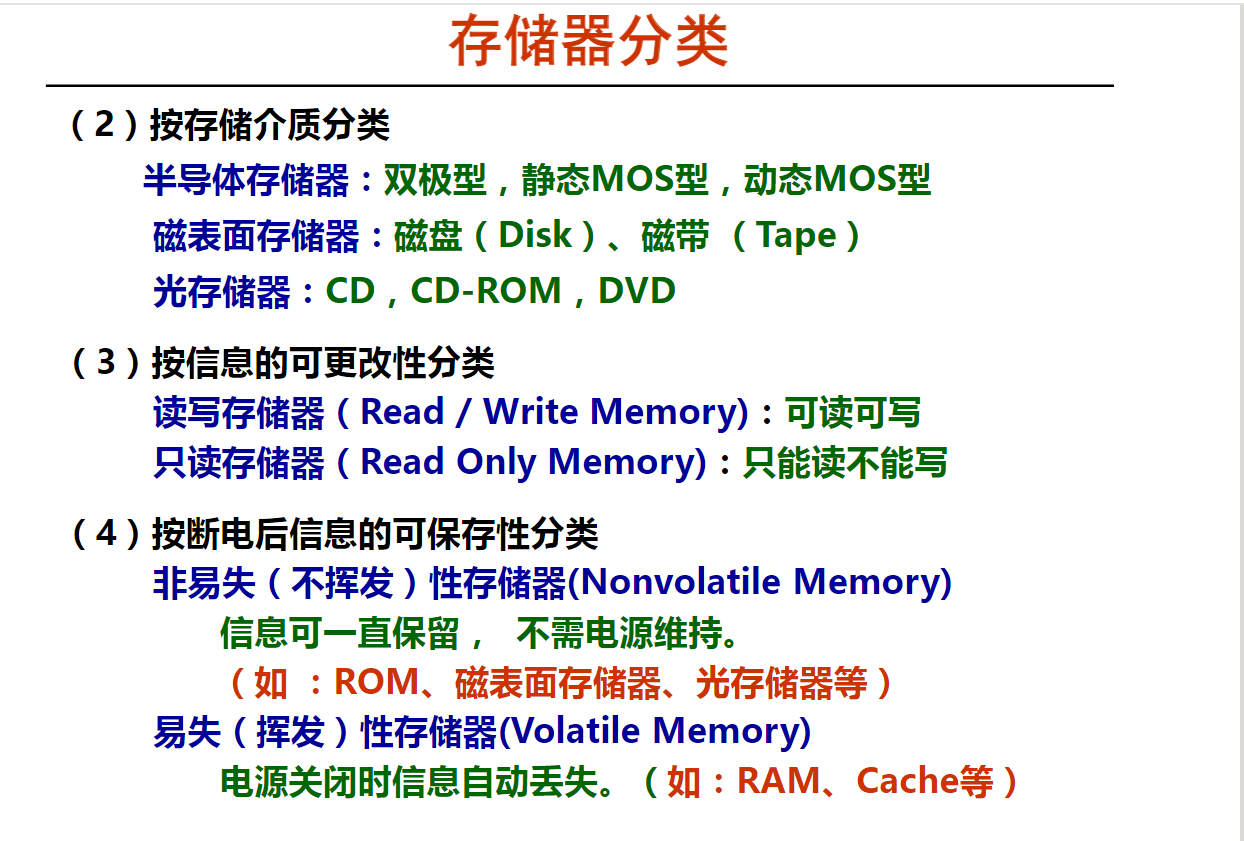

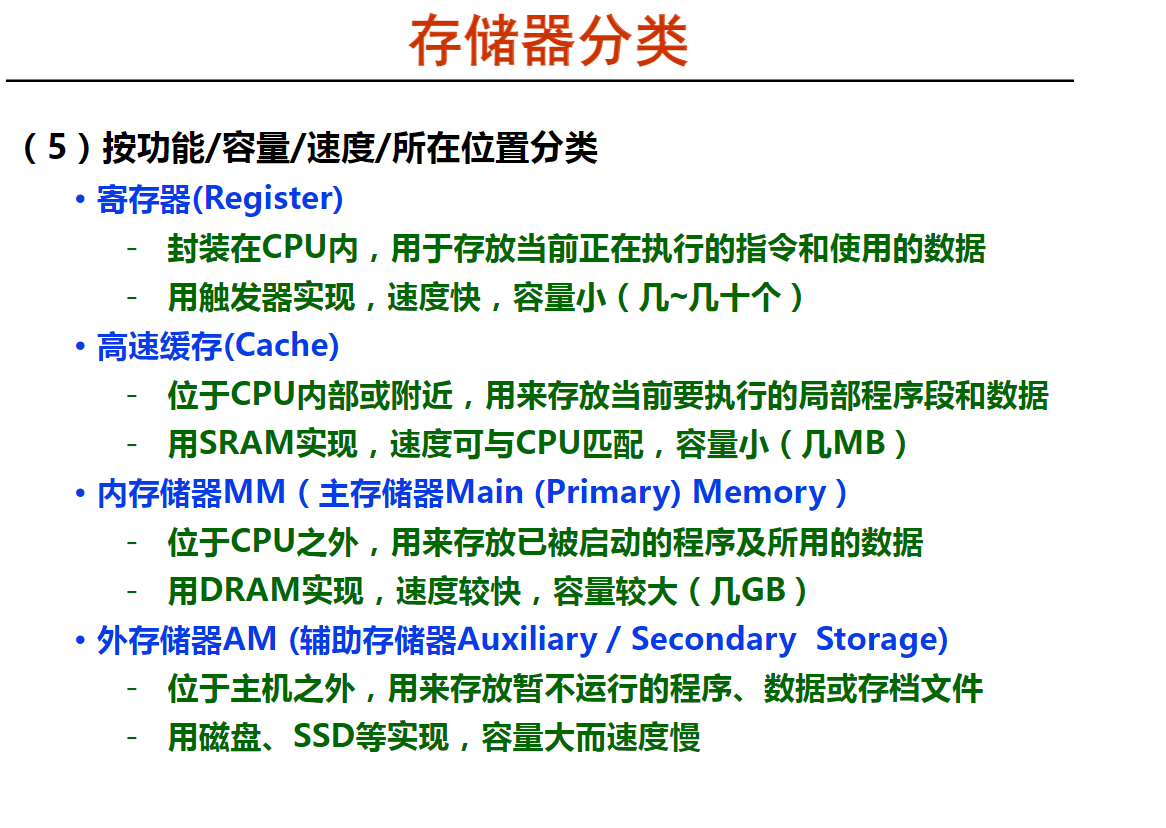

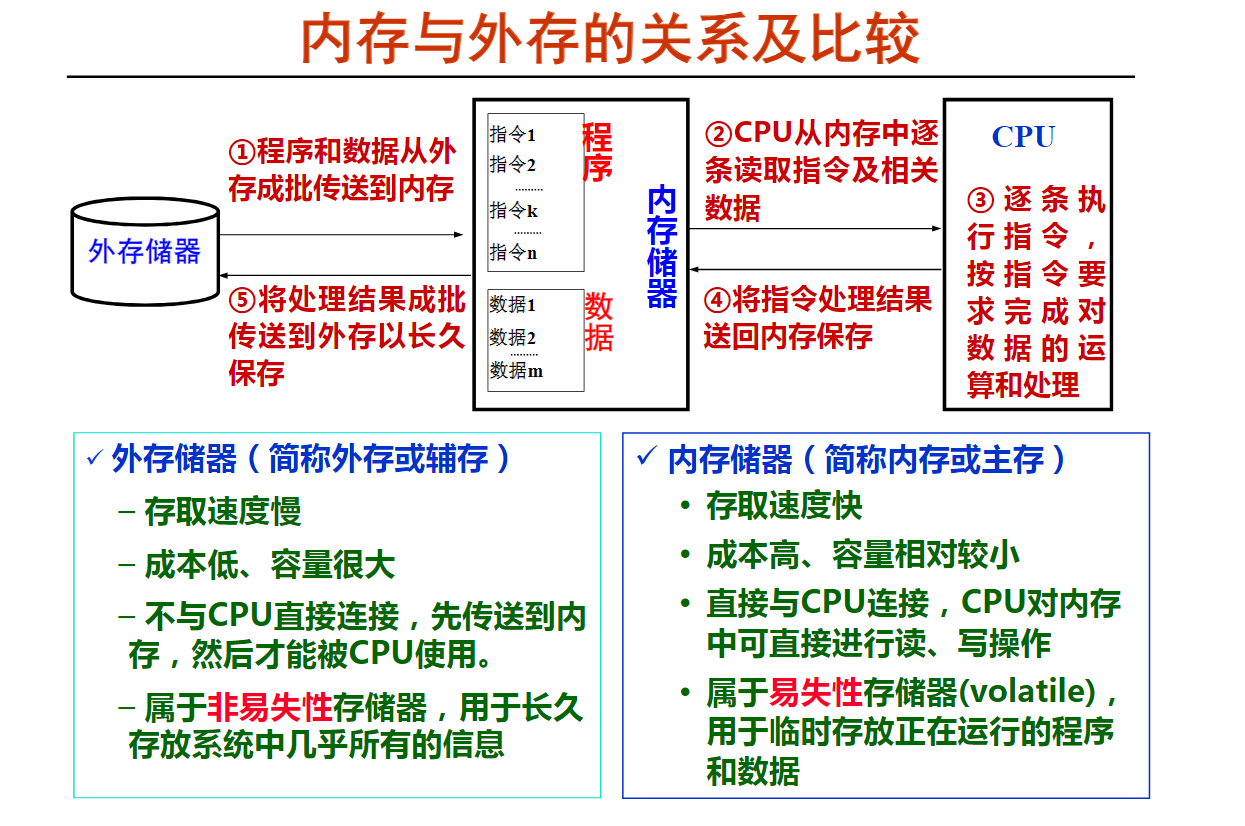

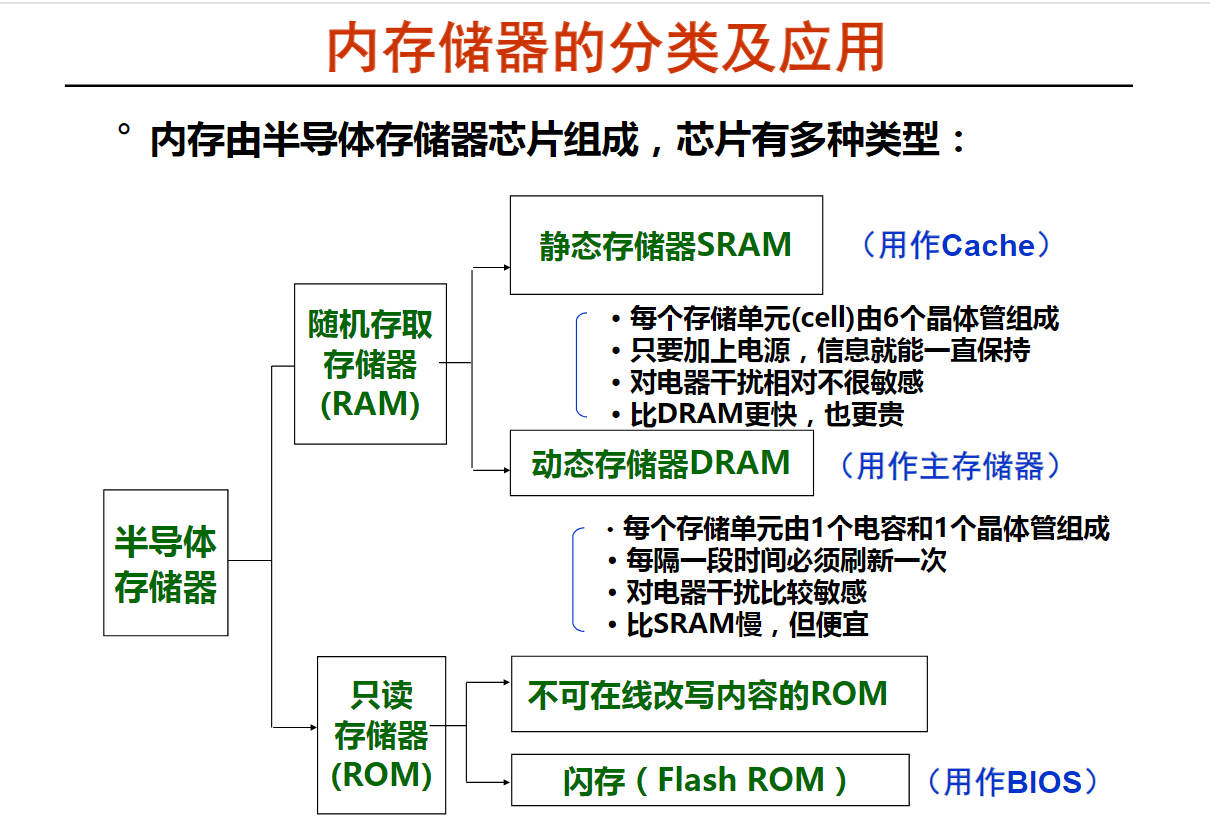

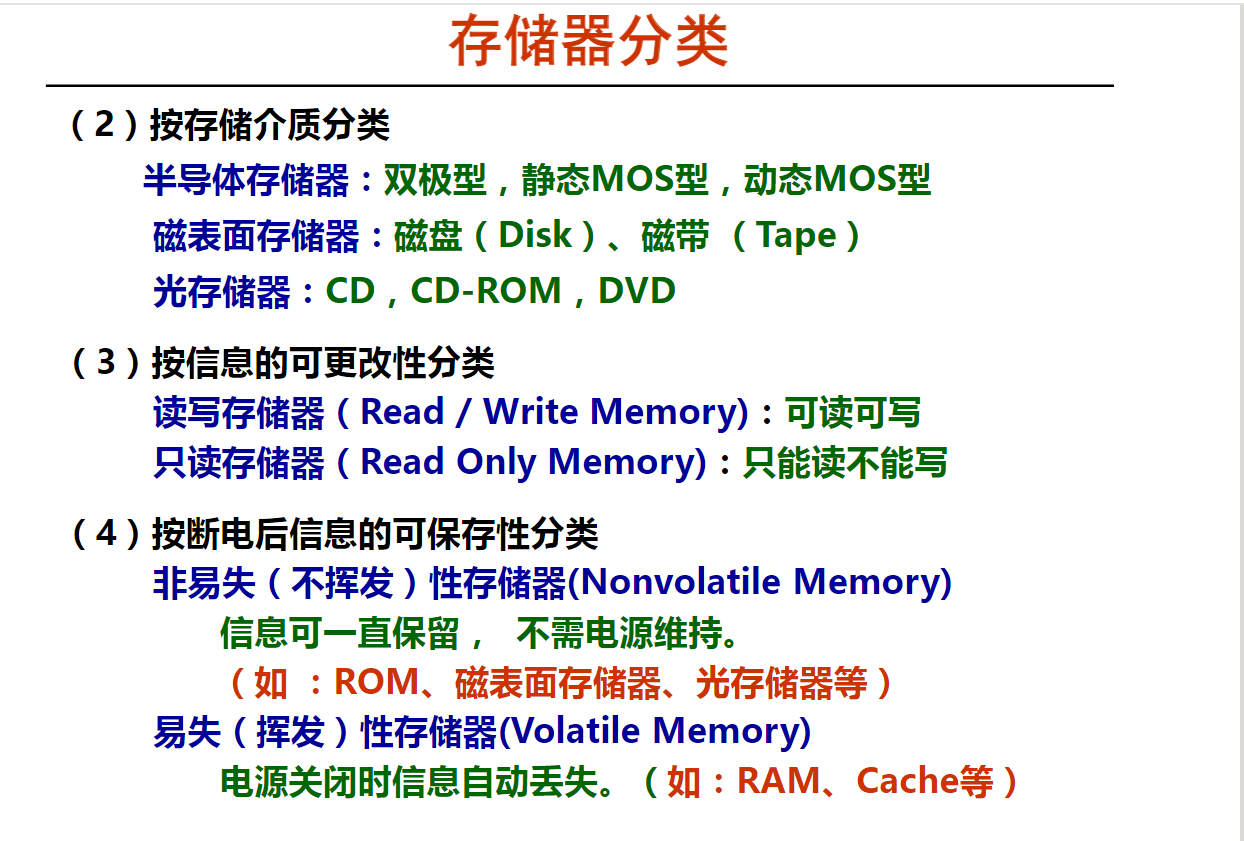

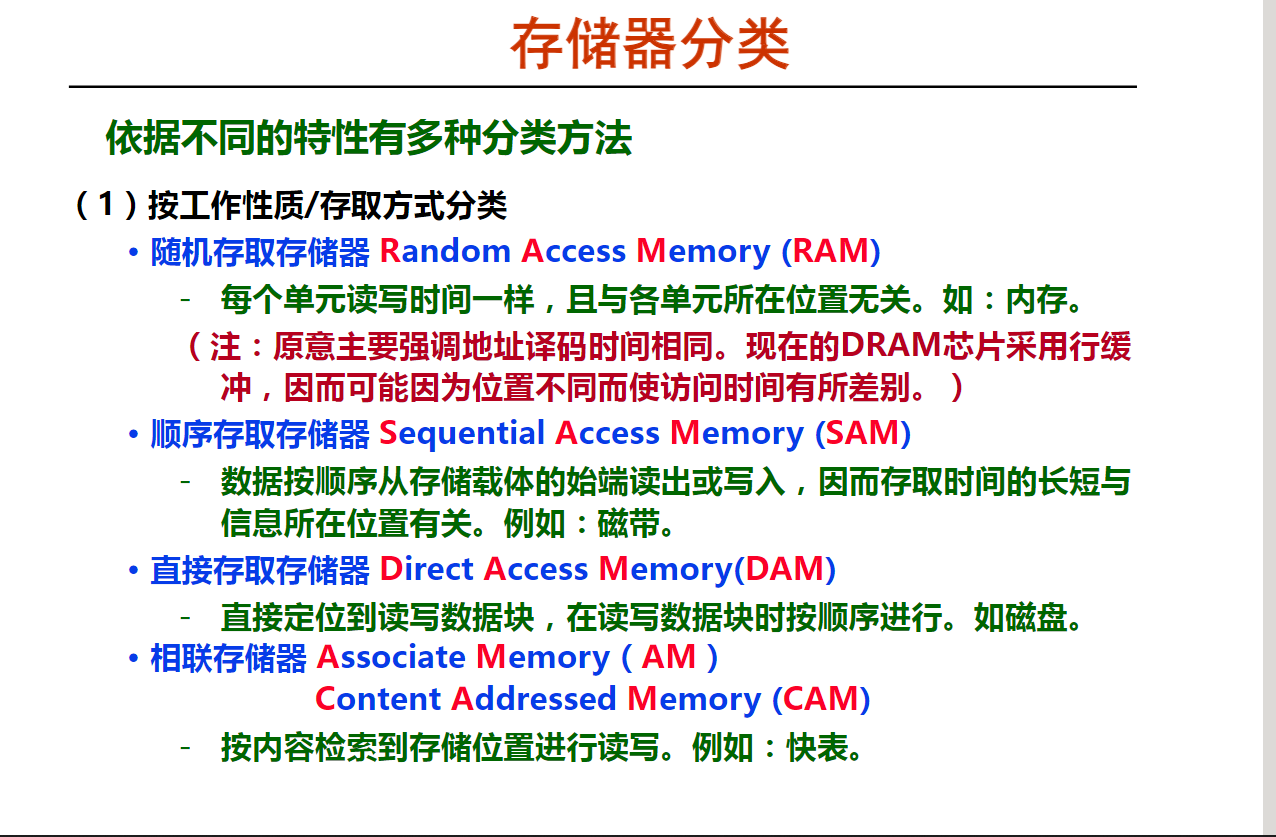

存储器分类

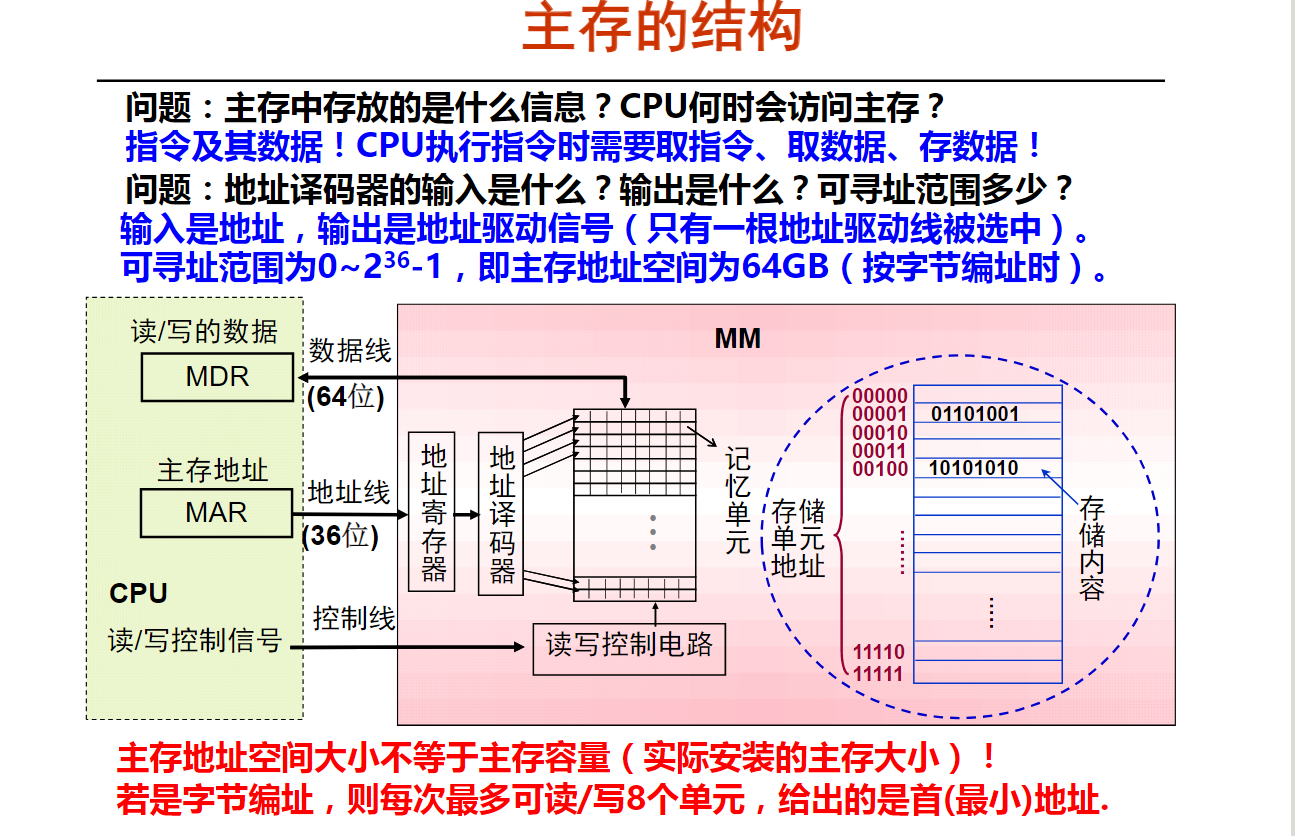

第2讲 主存的基本结构

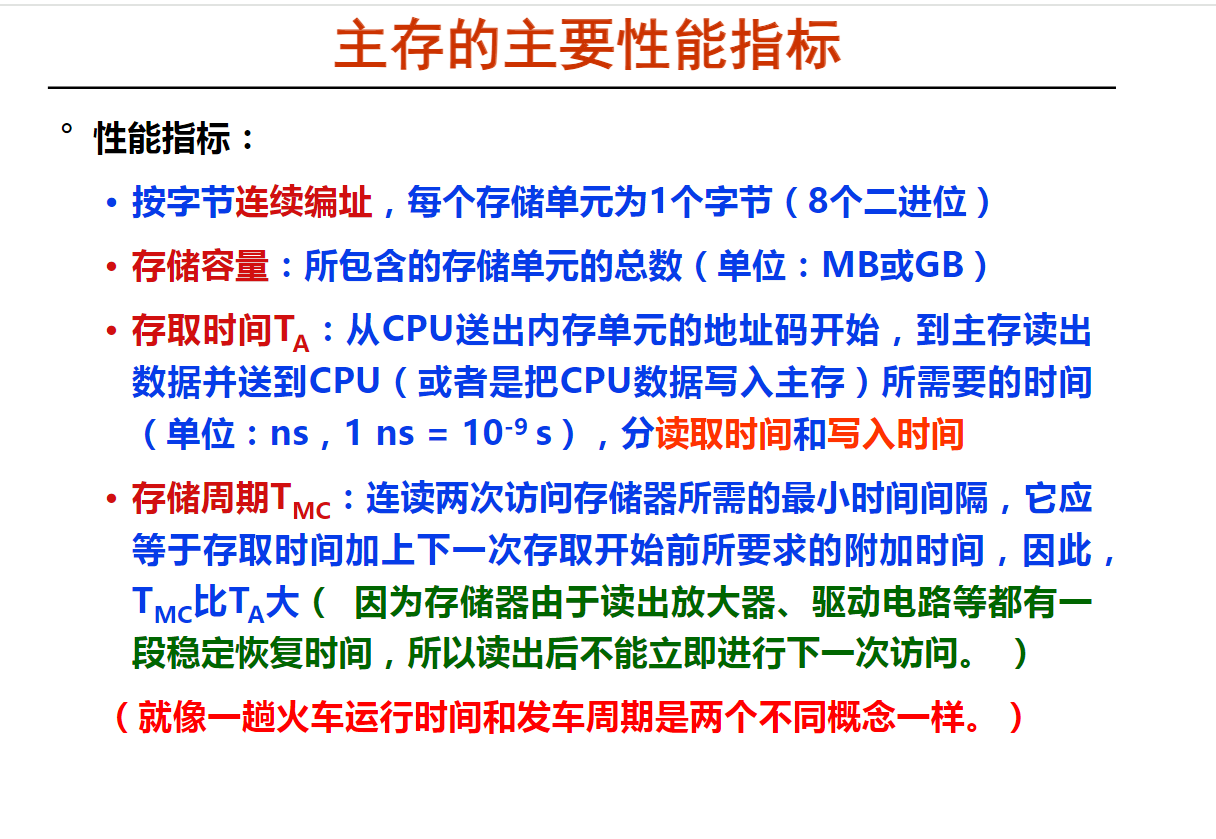

第3讲 主存的性能指标

第4讲 半导体存储器组织

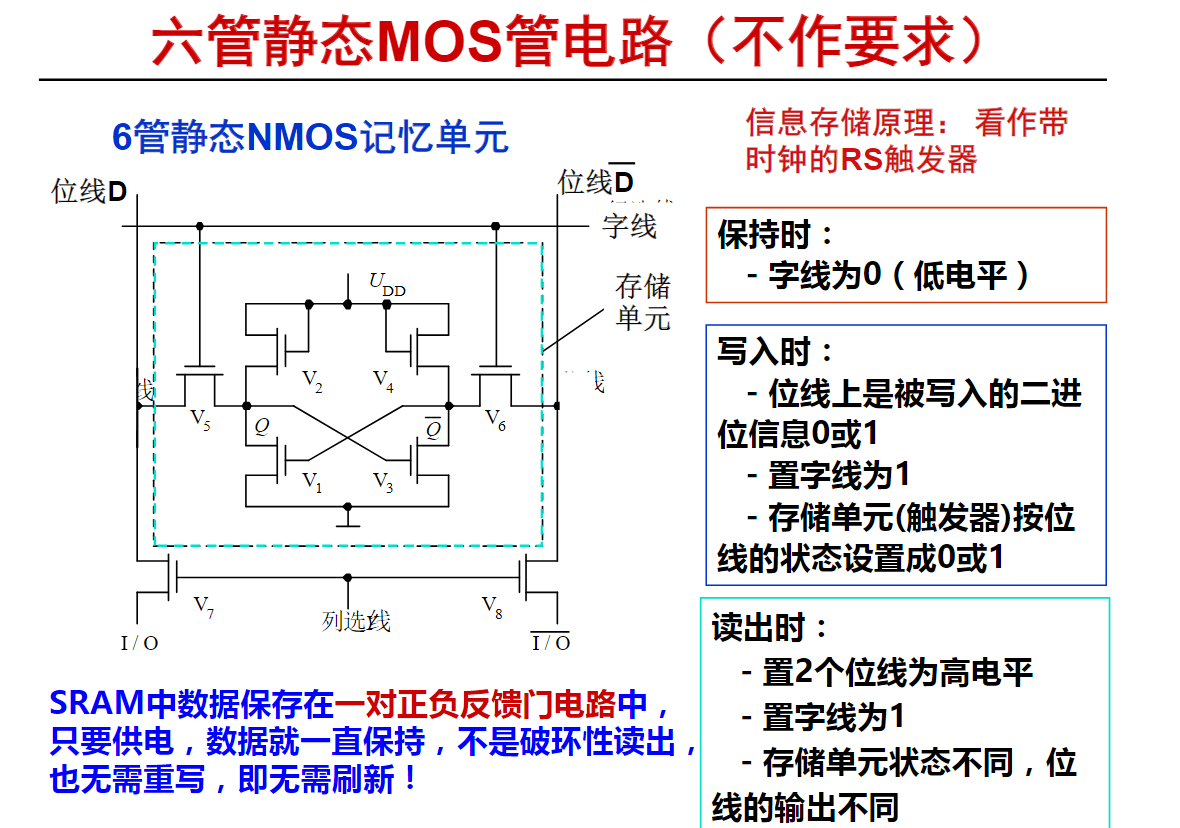

六管静态MOS管电路(4m32s)

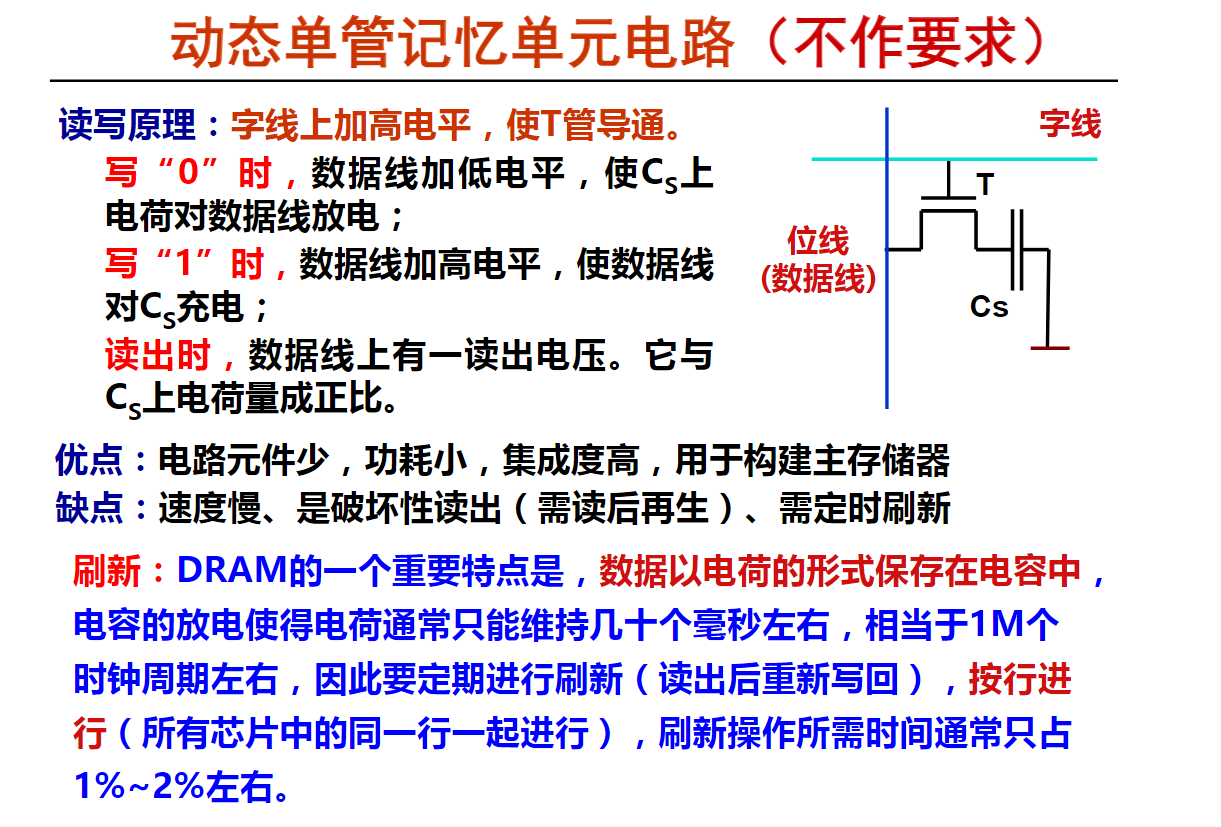

单管动态记忆单元电路(3m55s)

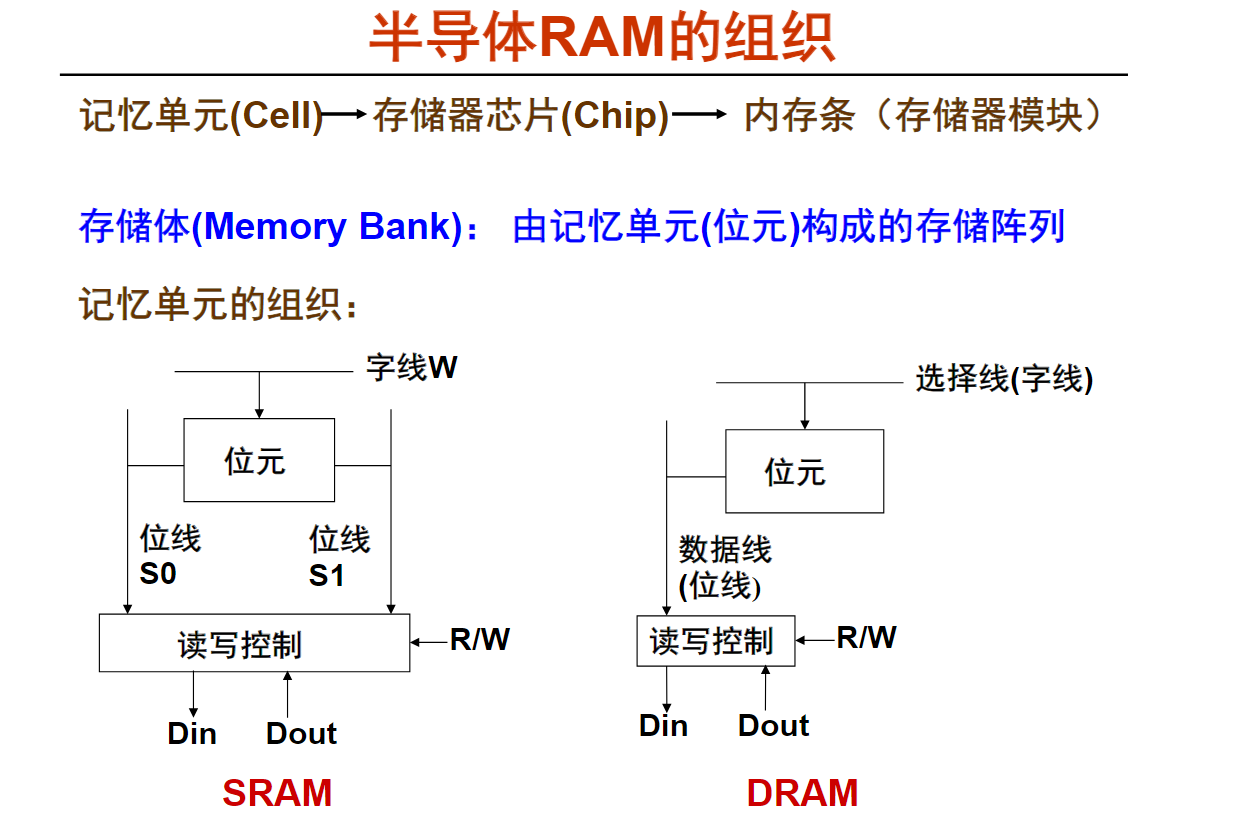

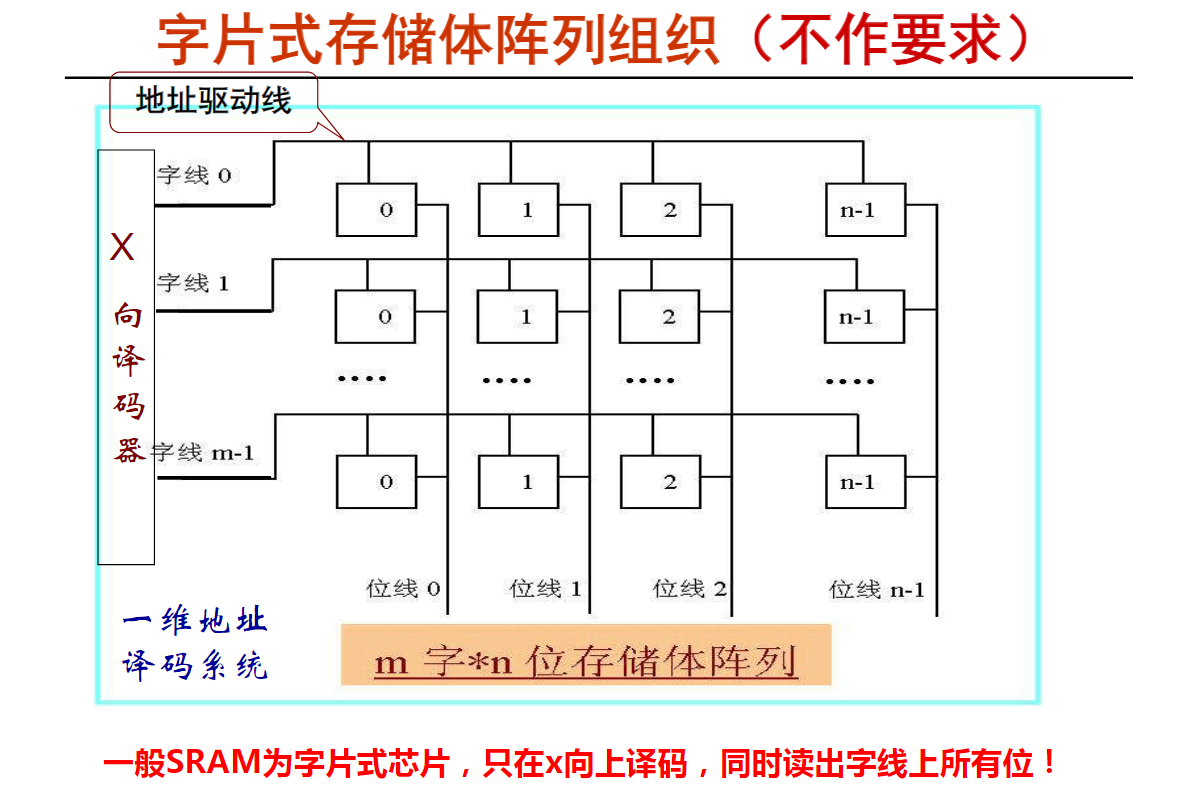

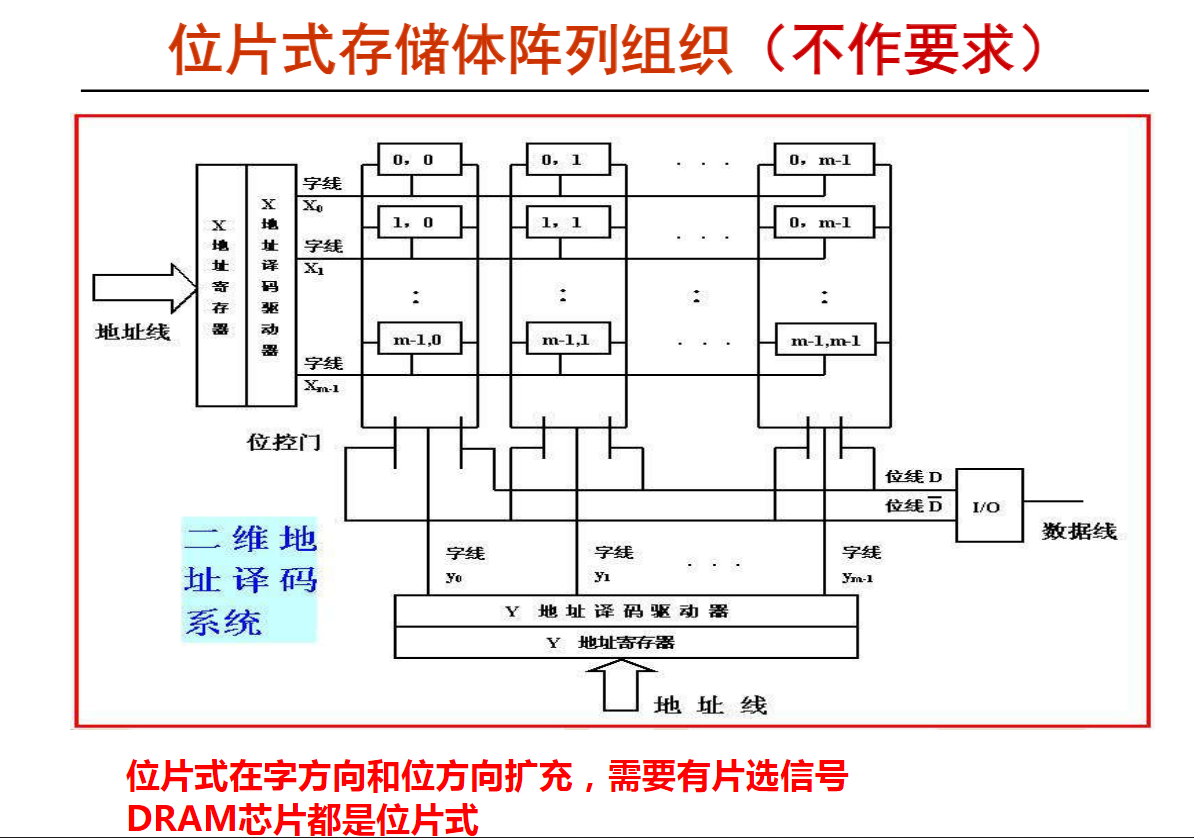

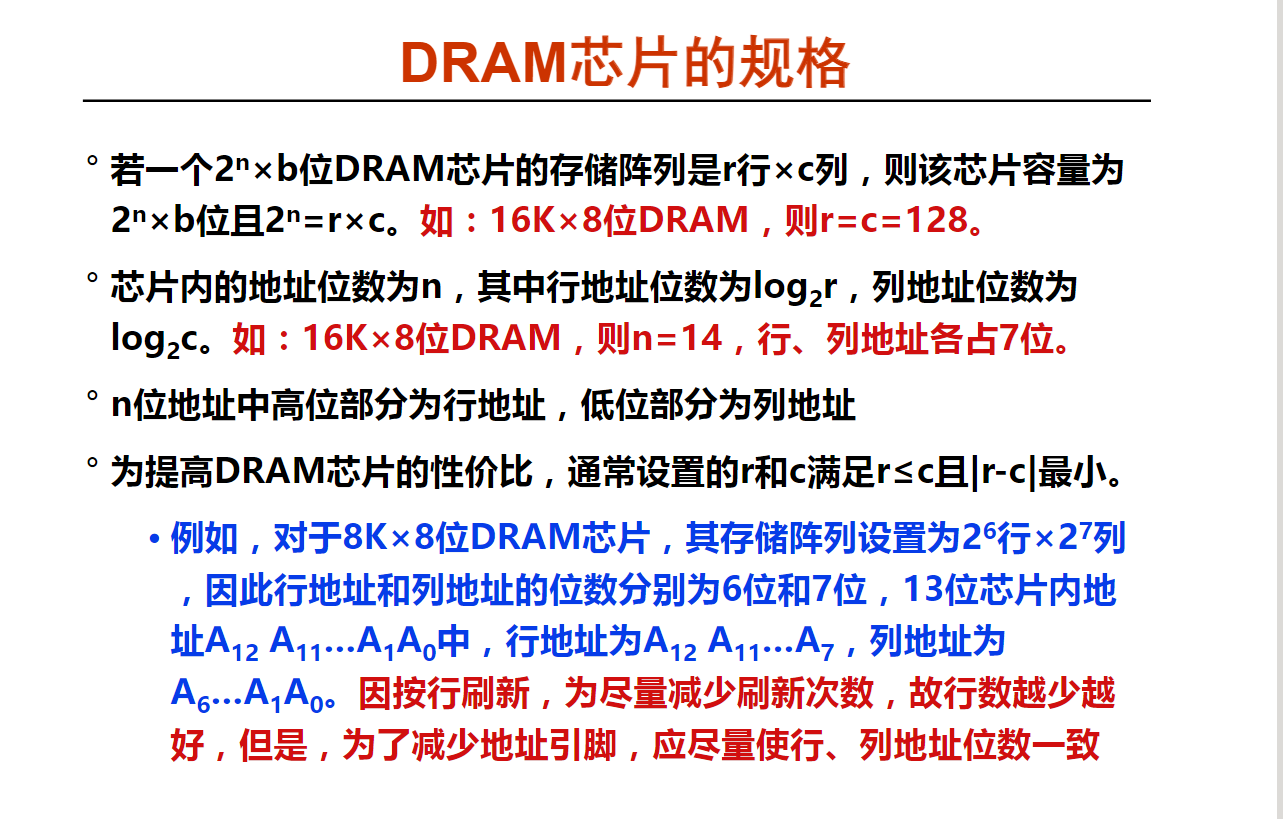

半导体RAM的组织(3m01s)

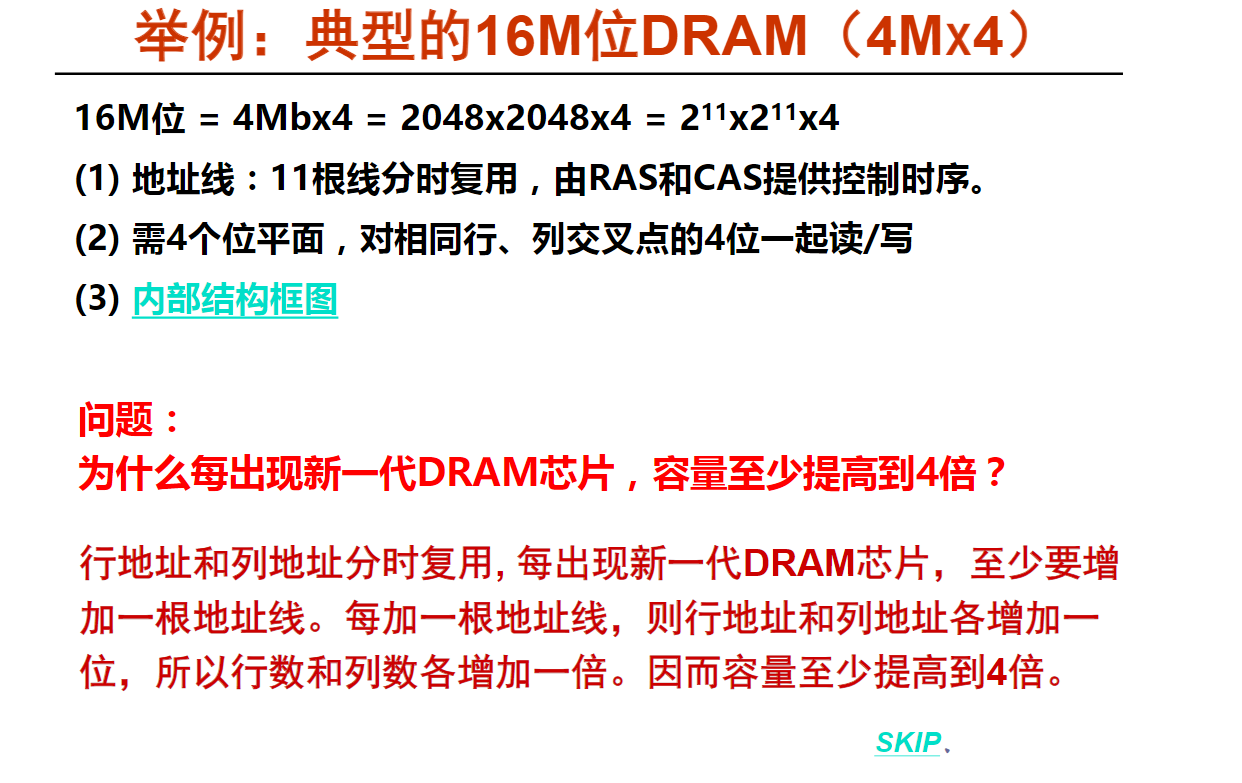

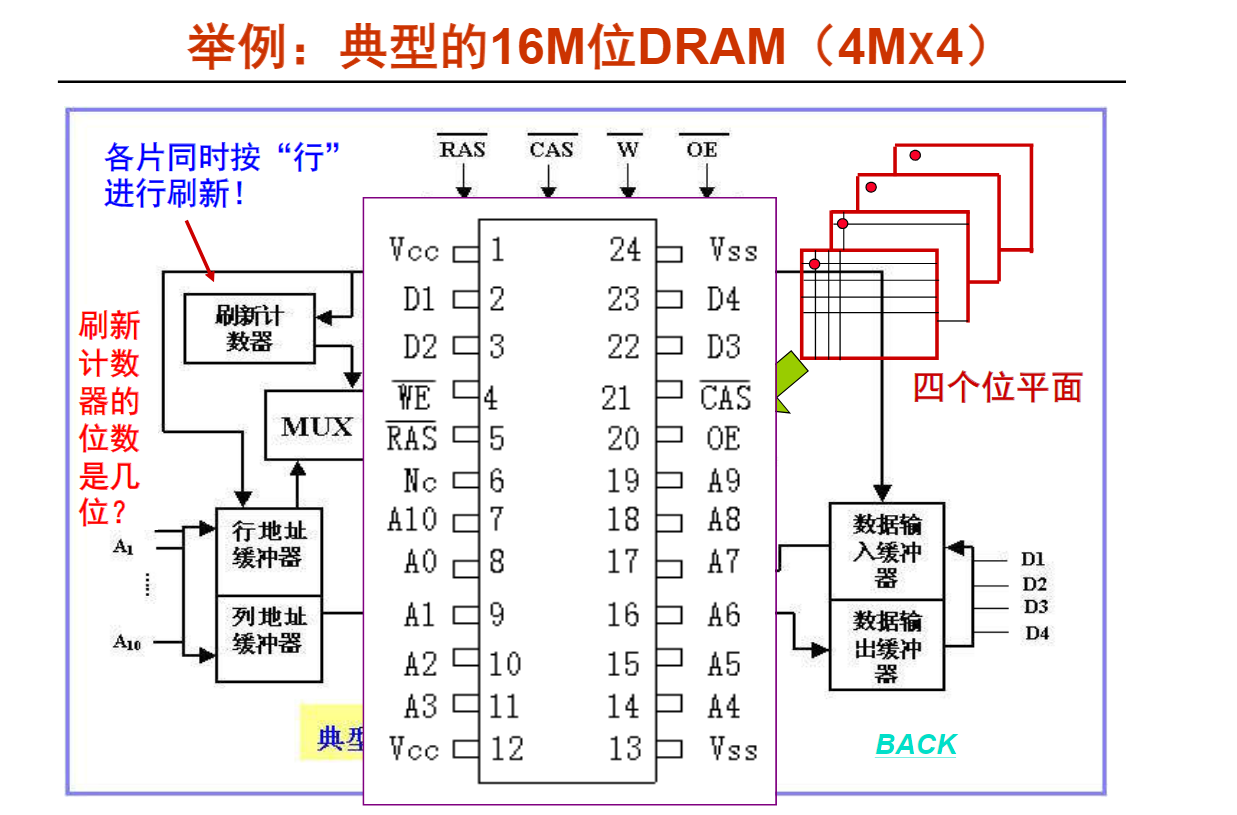

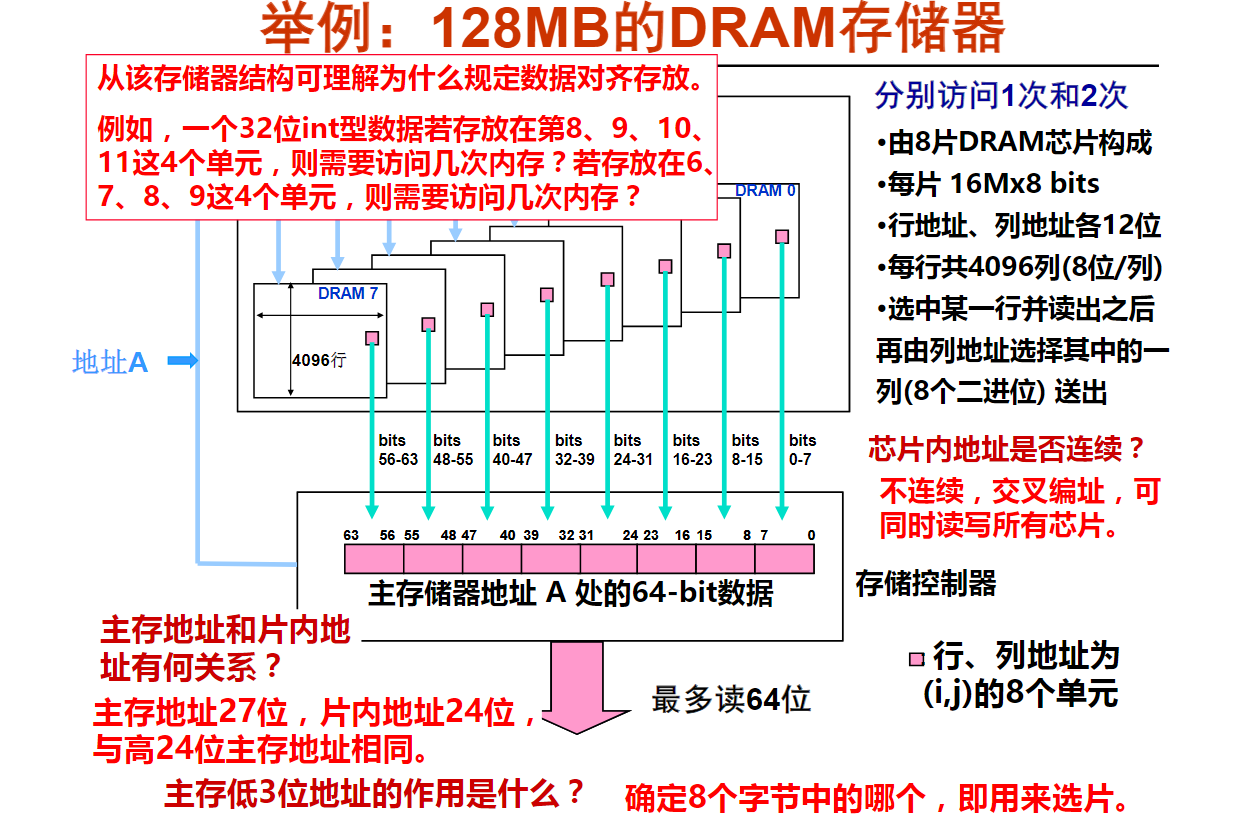

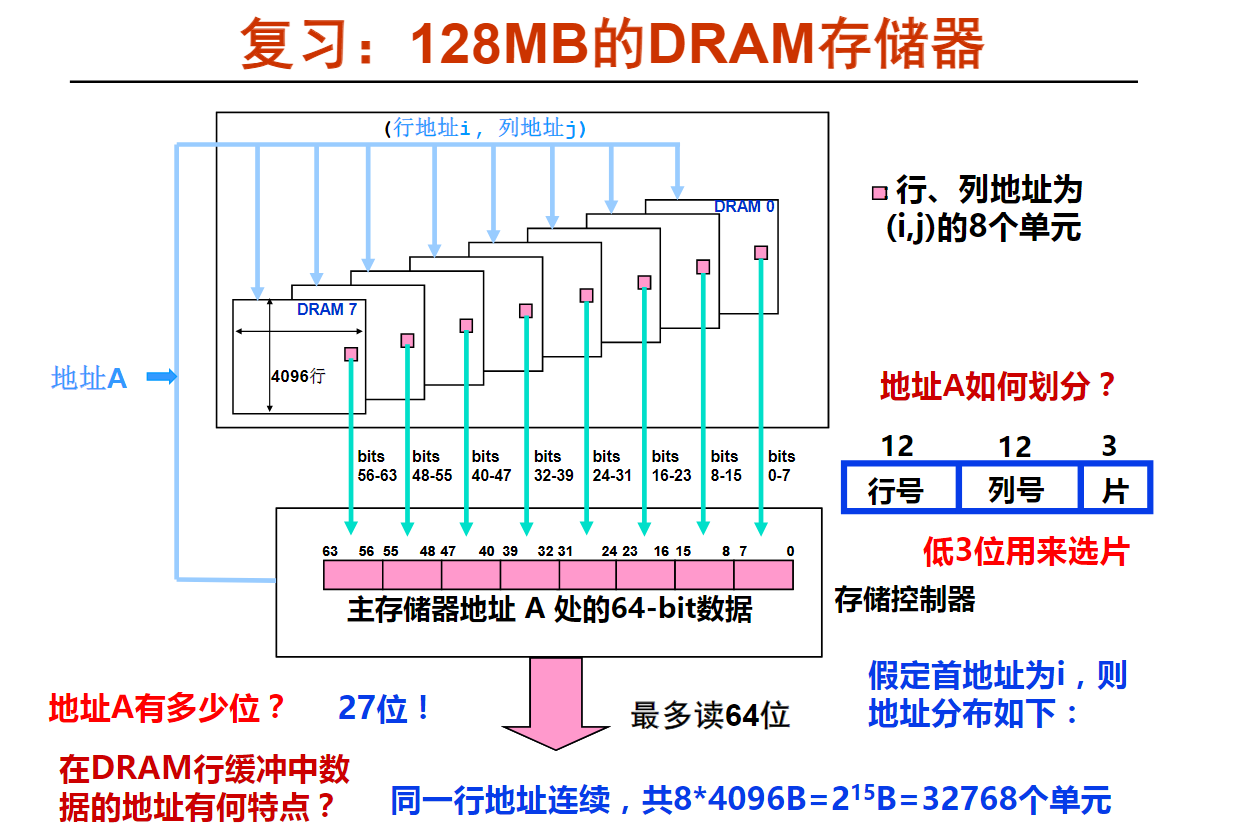

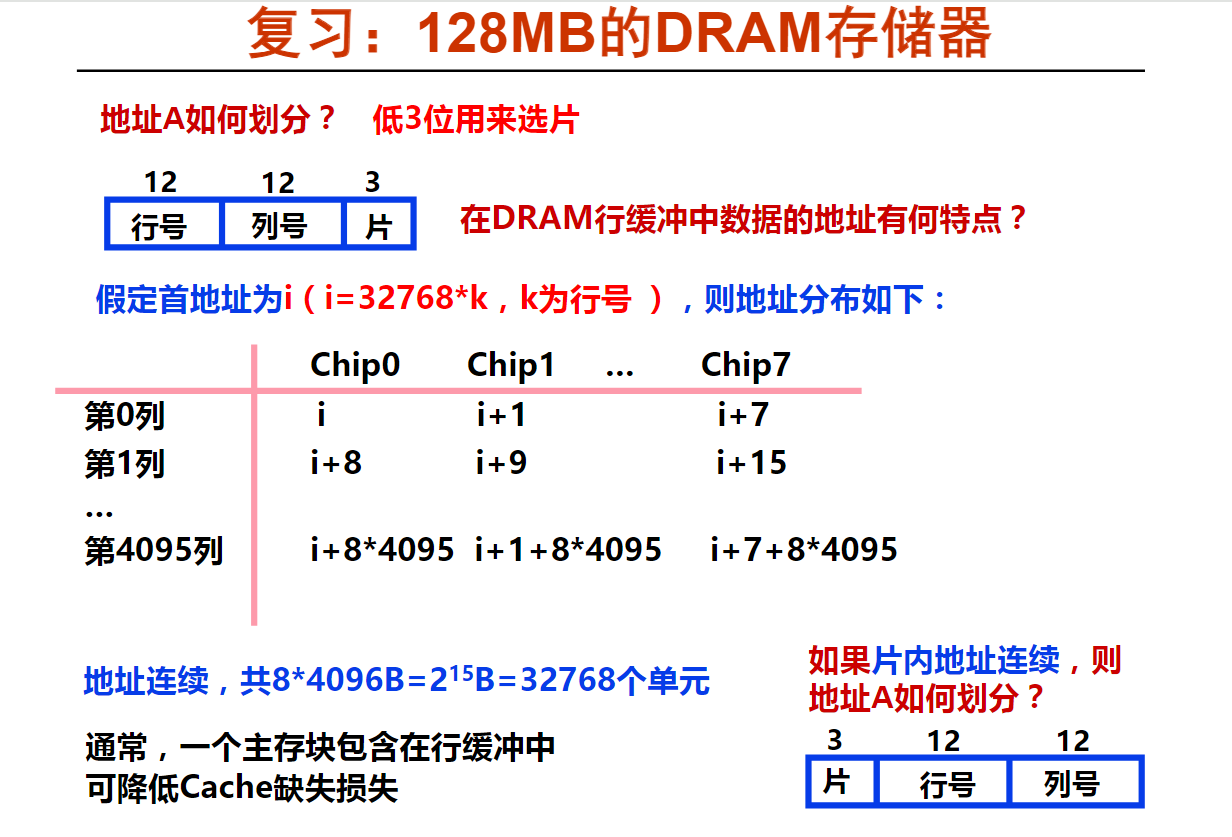

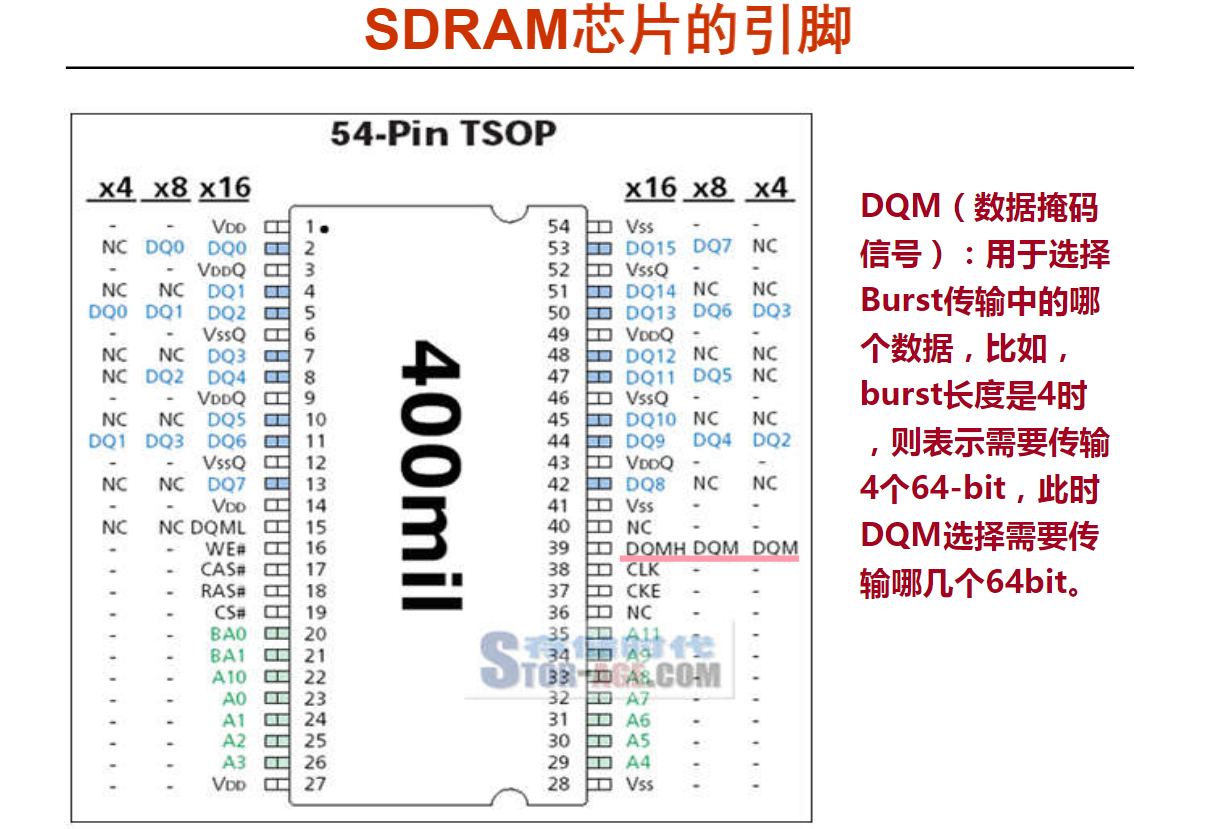

DRAM芯片举例

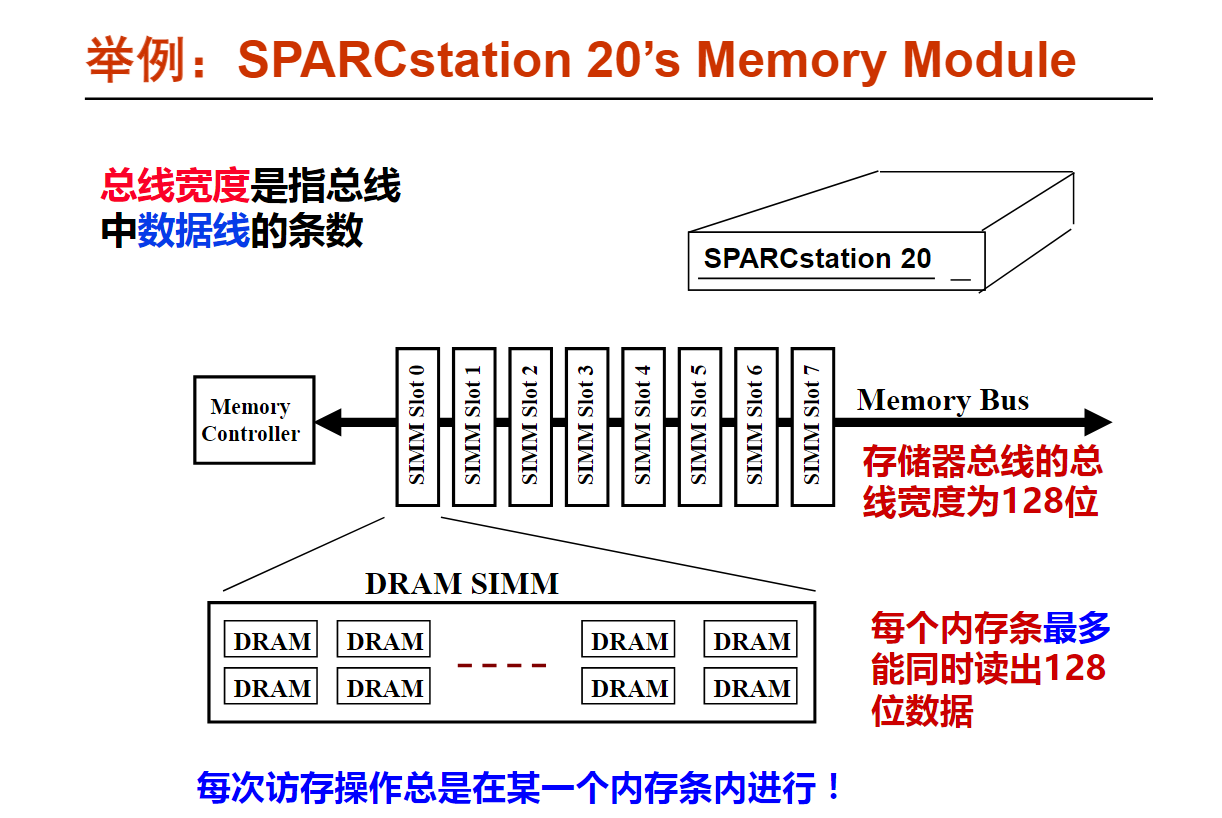

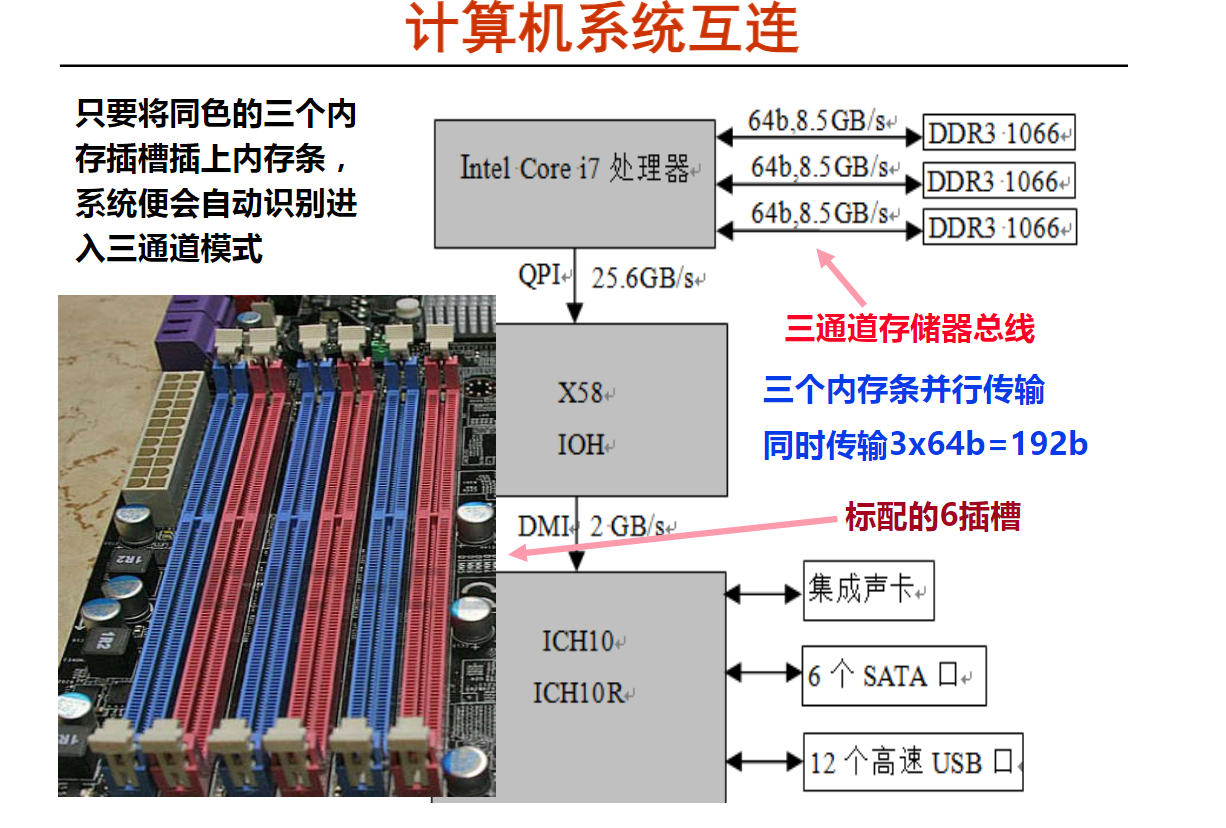

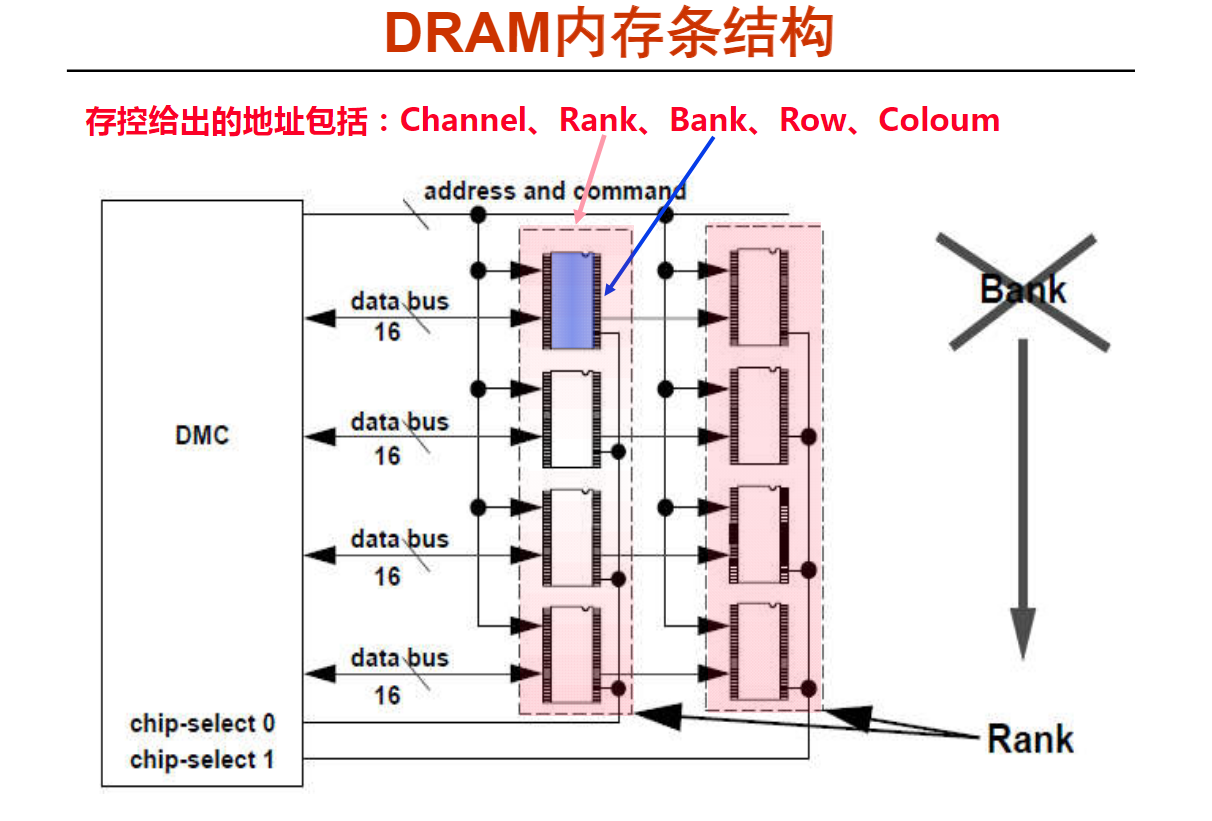

第5讲 内存条组织与总线宽度

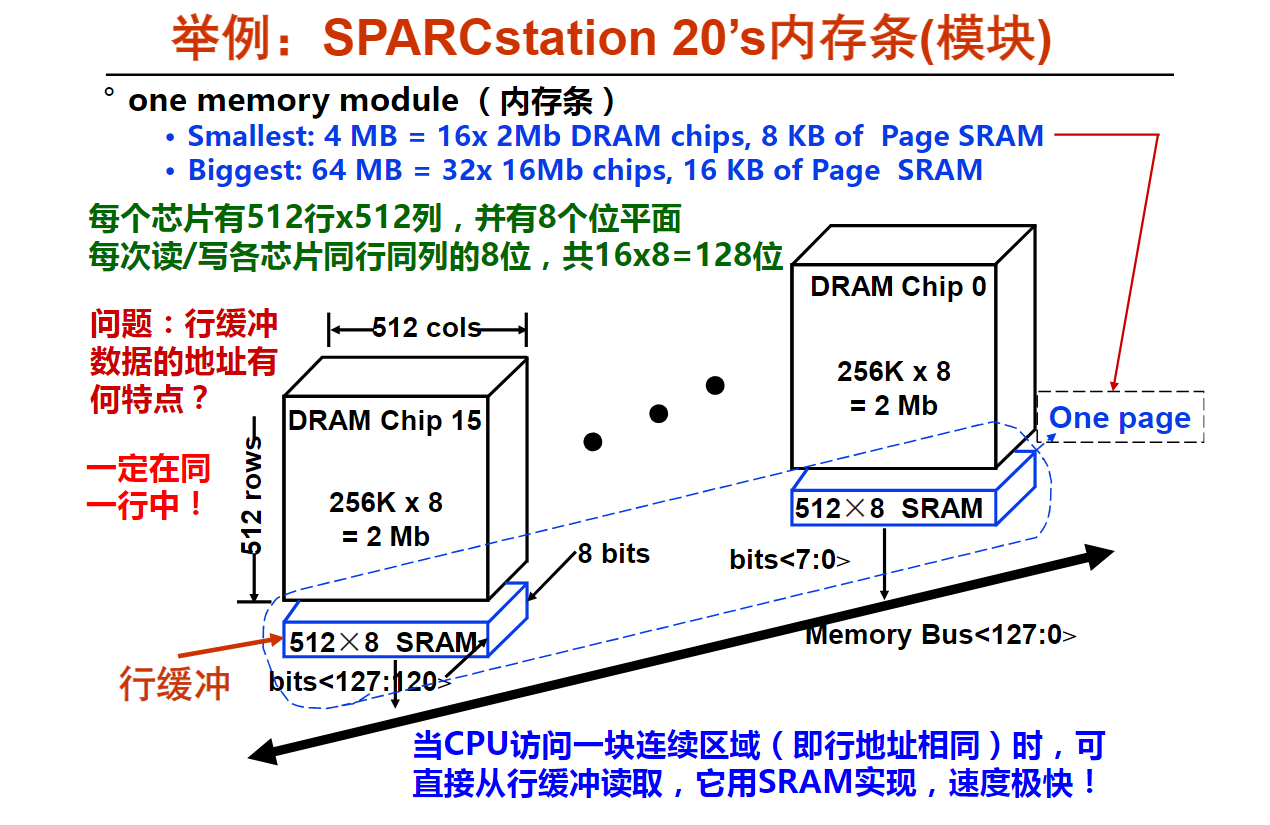

SPARC station 20的内存条(9m59s)

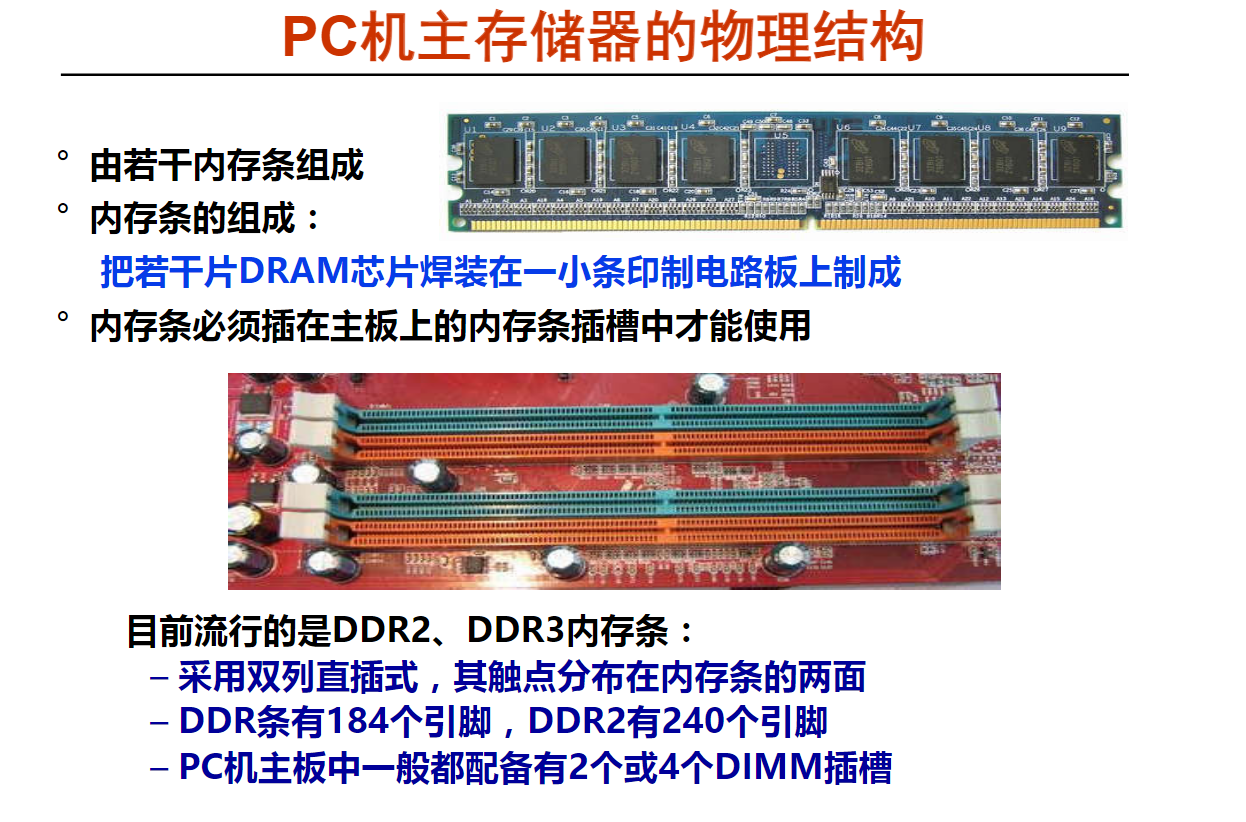

PC中的内存条(4m18s)

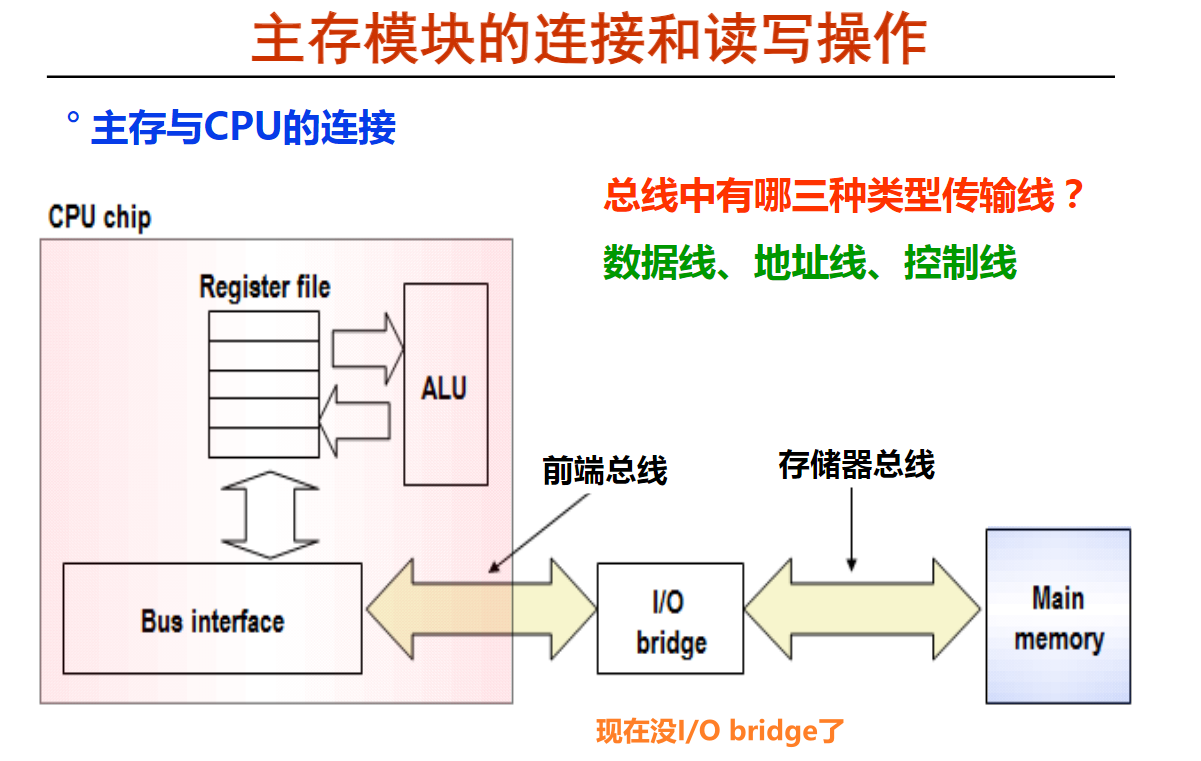

内存条与CPU的连接(6m24s)

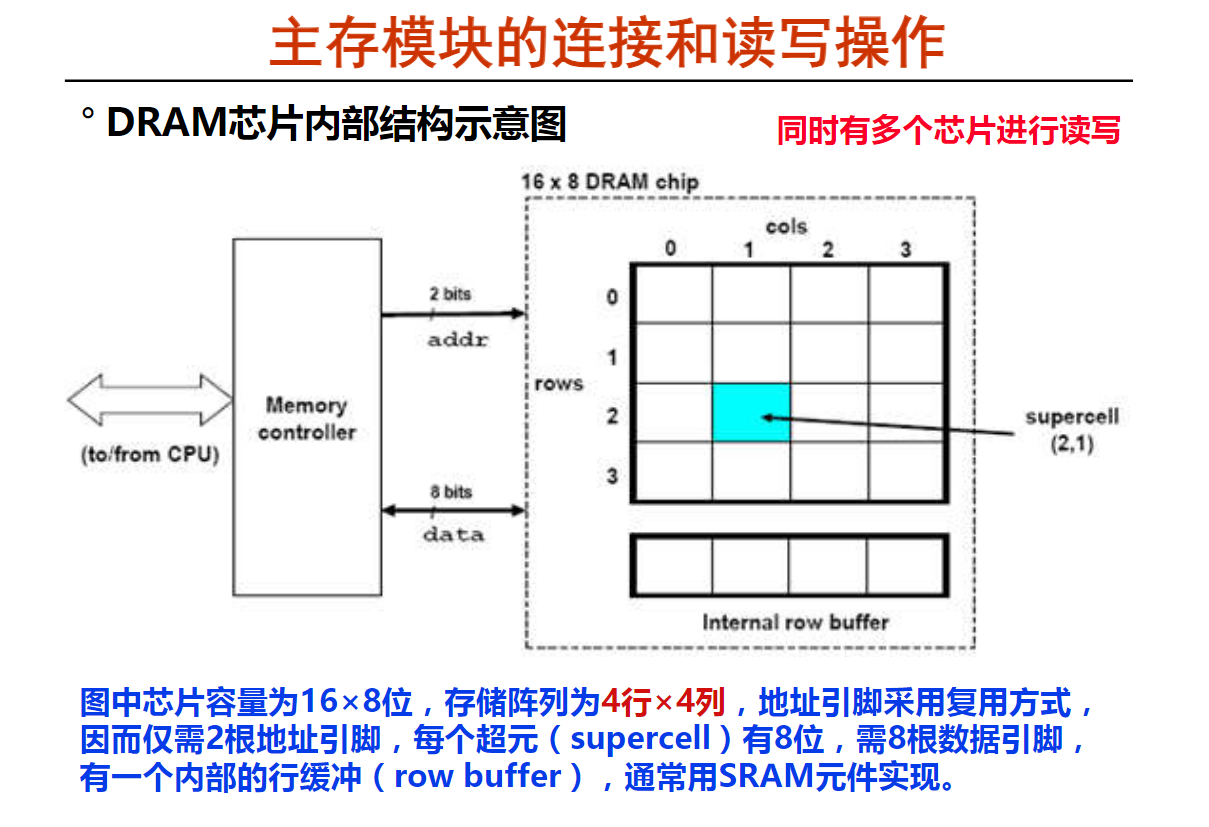

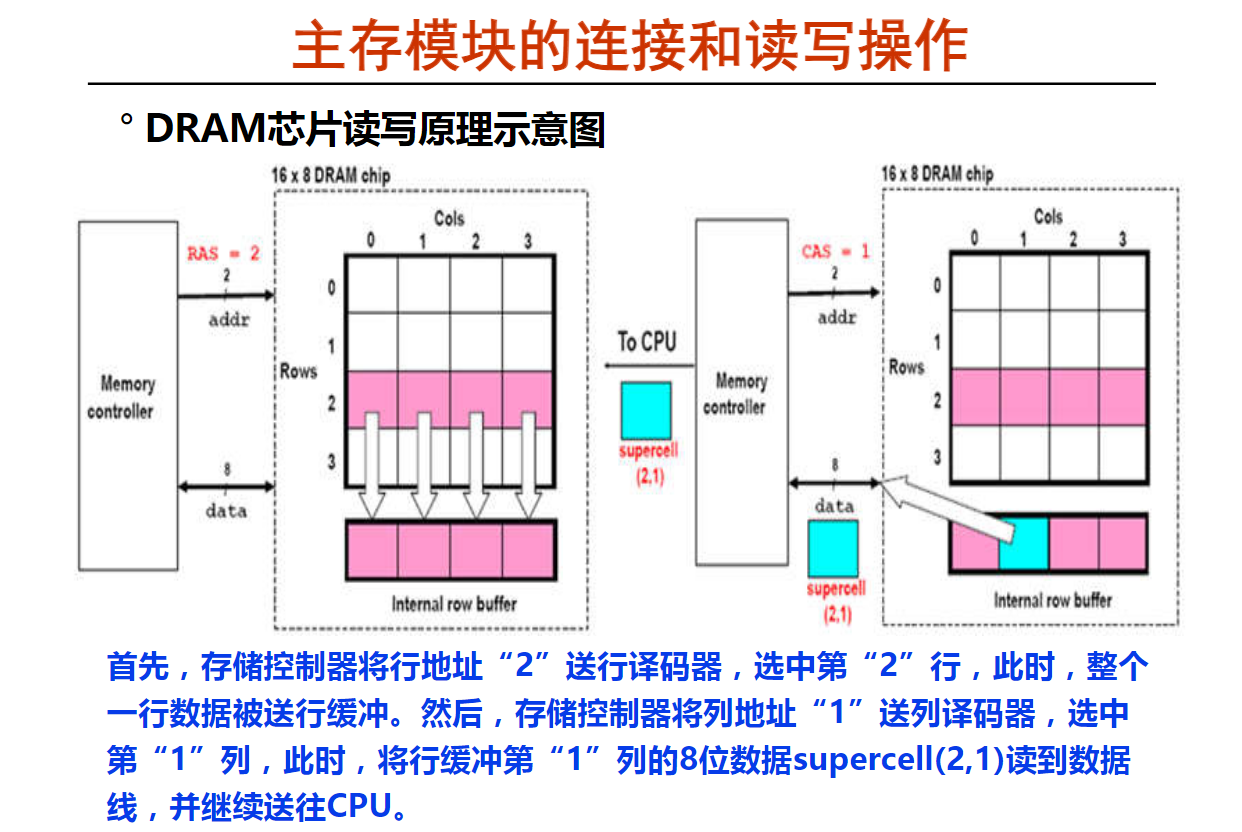

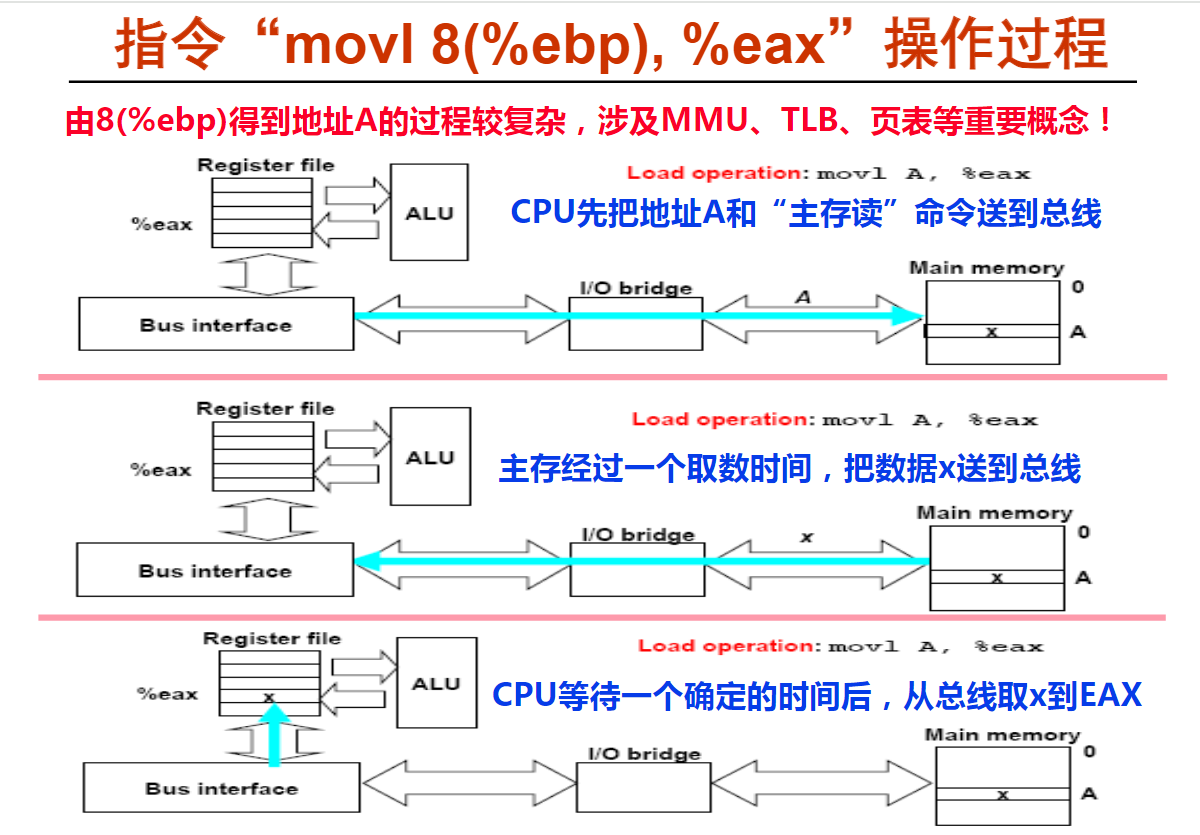

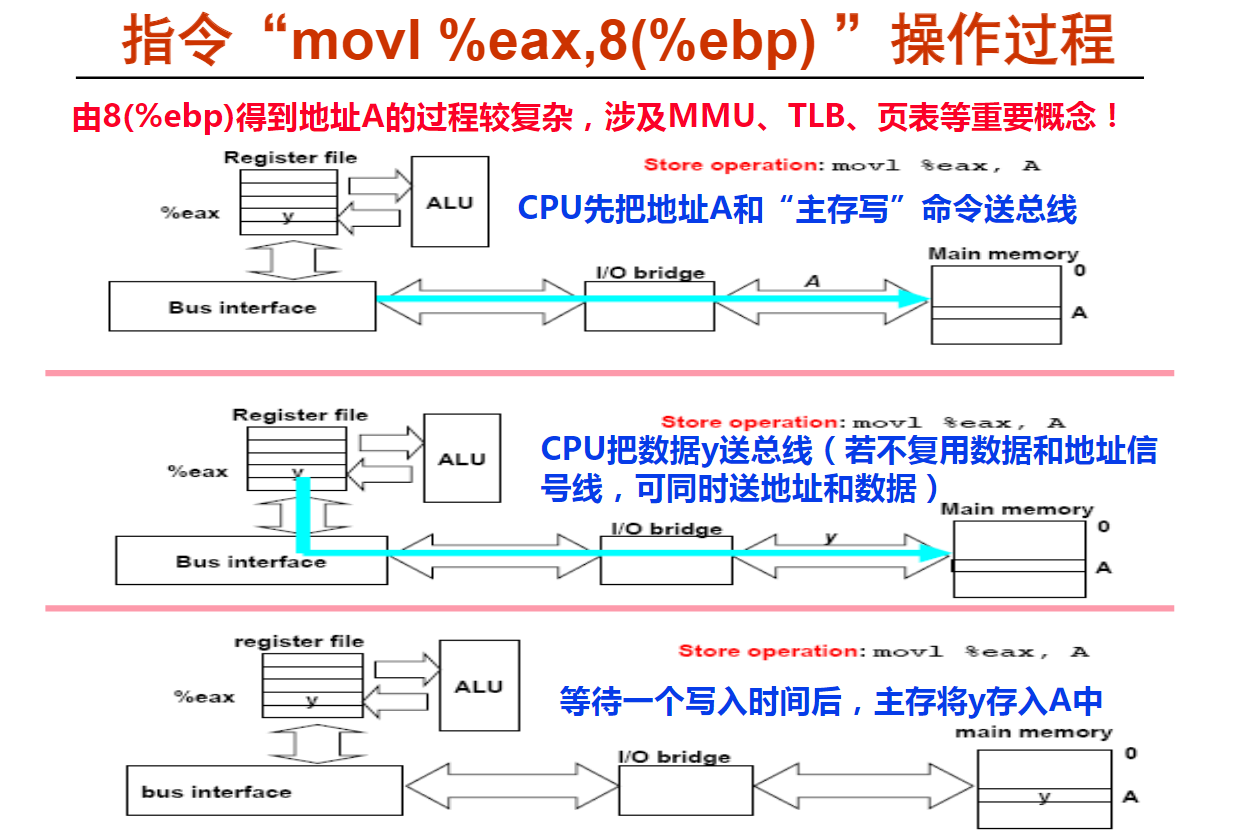

第6讲 主存模块的连接与读写操作(4m08s)

第二周小测验

错题序号:10

1下列几种存储器中,( C )是易失性存储器。

A.CD-ROM

B.Flash Memory

C.cache

D.EPROM

正确答案:C

2下面有关半导体存储器组织的叙述中,错误的是( B )。

A.每个存储单元有一个编号,就是存储单元的地址

B.同一个存储器中,每个存储单元的宽度可以不同

C.存储器的核心部分是存储阵列,由若干存储单元构成

D.存储单元由若干个存放0或1的记忆单元(cell)构成

解析: B、现代计算机的主存储器由半导体存储器构成,其中存放信息的地方称为存储阵列;每个存储阵列包含若干个存储单元,每个存储单元由若干个记忆单元(cell)构成,每个记忆单元存放一位信息(0或1)。

某一台计算机的主存储器编址方式,总是由其对应的指令集体系结构(ISA)确定的;现代通用计算机大多采用按字节编址方式,即主存储器中每个字节有一个地址,也即每个存储单元的宽度都是8位。

3若某个内存条容量为1GB,则说明该内存条中可存储( C )个字节。

A.10^30

B.10^9

C.2^30

D.2^9

正确答案:C你选对了

4某32位计算机,主存地址为32位,按字节编址,则该计算机的主存地址范围是(C )。

A.1~4G

B.1~32G

C.0~(4G-1)

D.0~(32G-1)

解析: C、因为主存地址为32位,所以主存地址空间占2^32=4G个存储单元;因为按字节编址,因此,主存最大可存储的信息量为4GB=32Gbits。主存储器总是从0开始编号,因此存储单元的地址为0、1、2、……、2^32-1=4G-1。这里,4G-1=2^32-1=1 0000 0000 0000 0000 0000 0000 0000 0000 -1 = 1111 1111 1111 1111 1111 1111 1111 1111 = FFFF FFFFH。

5假定主存地址空间大小为1024MB,按字节编址,每次读写操作最多可以一次存取32位。不考虑其它因素,则存储器地址寄存器MAR和存储器数据寄存器MDR的位数至少应分别为( C )。

A.28,32

B.28,8

C.30,32

D.30,8

解析: C、因为1024M=2^30,所以MAR至少为30位。

6采用行、列地址引脚复用的半导体存储器芯片是( B )。

A.SRAM

B.DRAM

C.EPROM

D.Flash Memory

正确答案:B你选对了

7下面有关ROM和RAM的叙述中,错误的是( B )。

A.ROM和RAM都采用随机访问方式进行读写

B.计算机系统的主存都用DRAM芯片实现

C.计算机系统的主存由RAM和ROM组成

D.RAM是可读可写存储器,ROM是只读存储器

正确答案:B你选对了

8下面有关半导体存储器的叙述中,错误的是(A )。

A.半导体存储器都采用随机存取方式进行读写

B.SRAM是半导体静态随机访问存储器,可用作cache

C.ROM芯片属于半导体随机存储器芯片

D.DRAM是半导体动态随机访问存储器,可用作主存

解析: A、有些情况下,可用半导体存储器实现相联存储器,即按内容进行访问,而不是按地址进行随机读写。

9存储容量为16K×4位的DRAM芯片,其地址引脚和数据引脚数各是( B )。

A.14和1

B.7和4

C.7和1

D.14和4

解析: B、因为DRAM芯片存储容量为16K×4位,故该芯片共有16K=2^14个存储单元,应该有14位地址,行、列地址引脚复用后,芯片的地址引脚数为7。每个存储单元占4位,因此芯片的数据引脚数为4。

10假定用若干个16K×8位的存储器芯片组成一个64K×8位的存储器,芯片各单元交叉编址,则地址BFFFH所在的芯片的最小地址为(A )。

A.0003H

B.0000H

C.0001H

D.0002H

解析: A、用若干个16K×8位的存储器芯片构成64K×8位的存储器,需要64K×8位/(16K×8位)= 4个芯片。因为采用交叉编址方式,所以,存储单元地址对4取模后,低两位相同的存储单元在同一个芯片中。BFFFH的最低两位为11,显然,与0003H在同一个芯片中。