第四周高速缓存概述

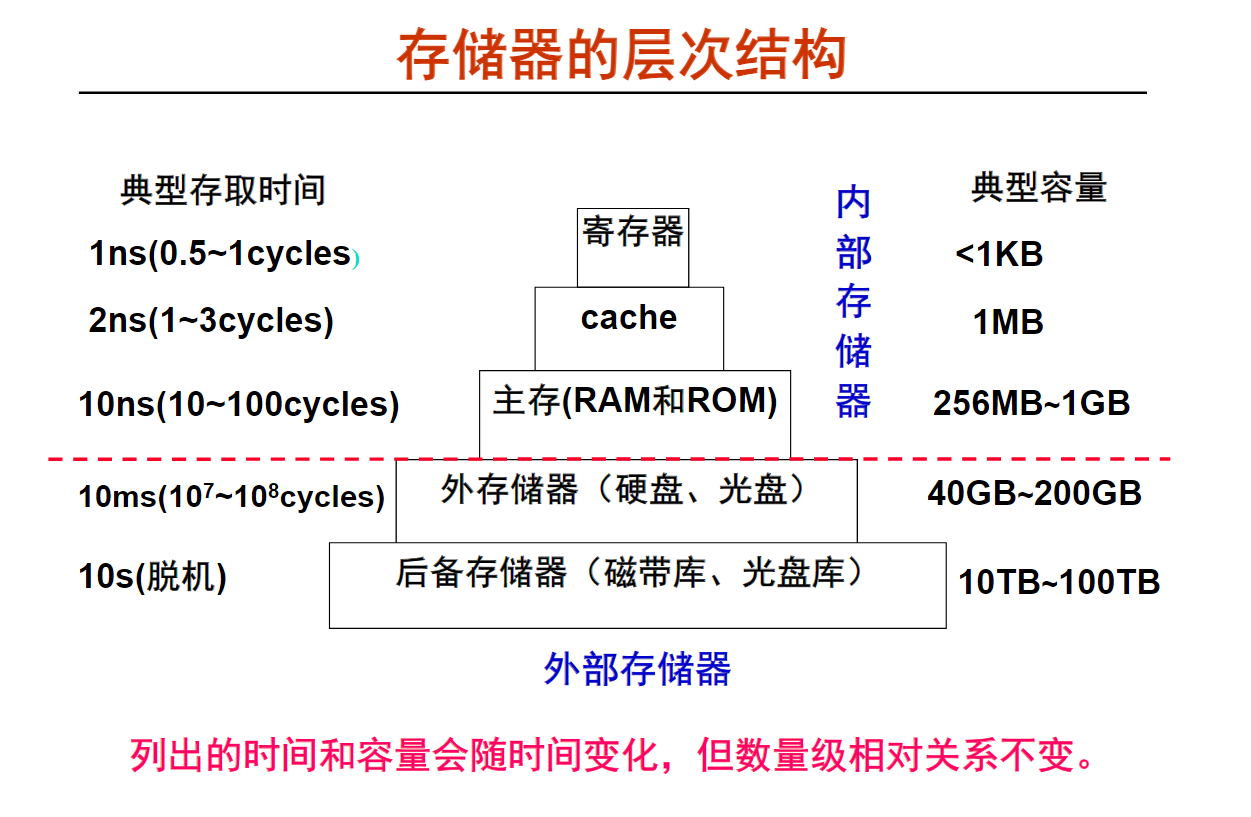

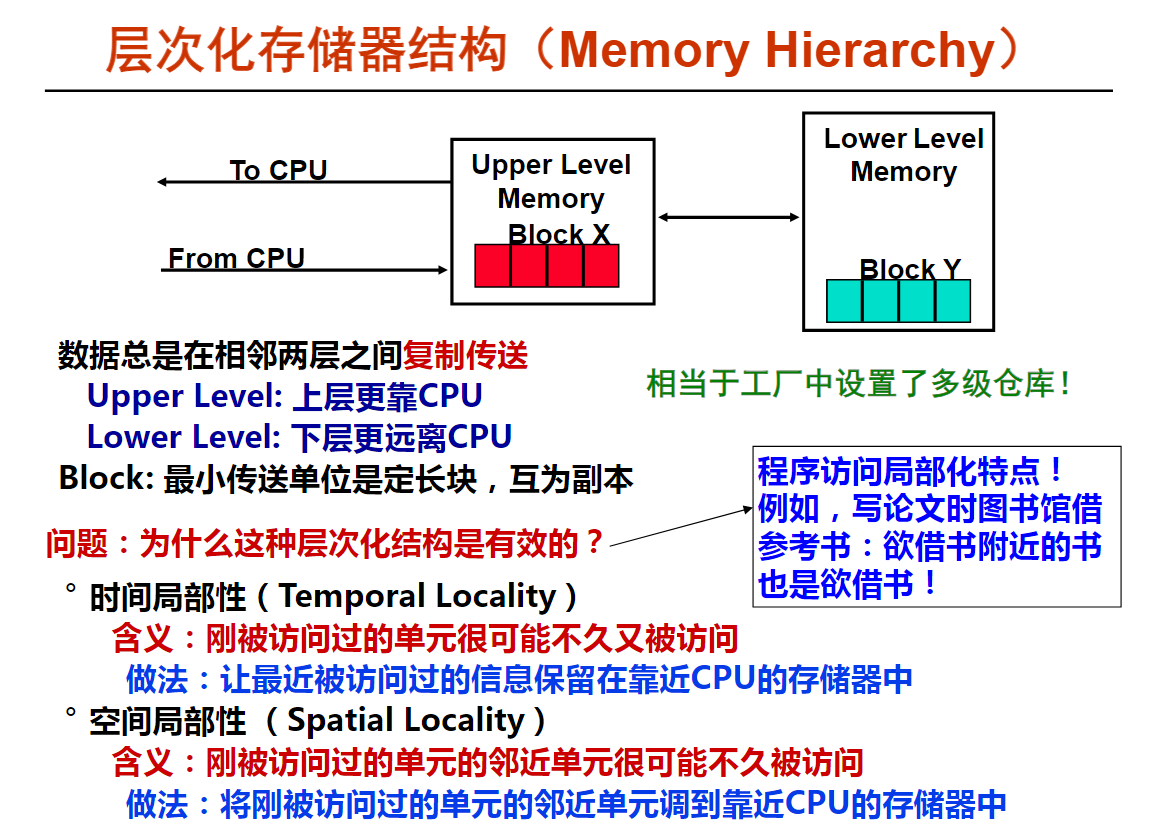

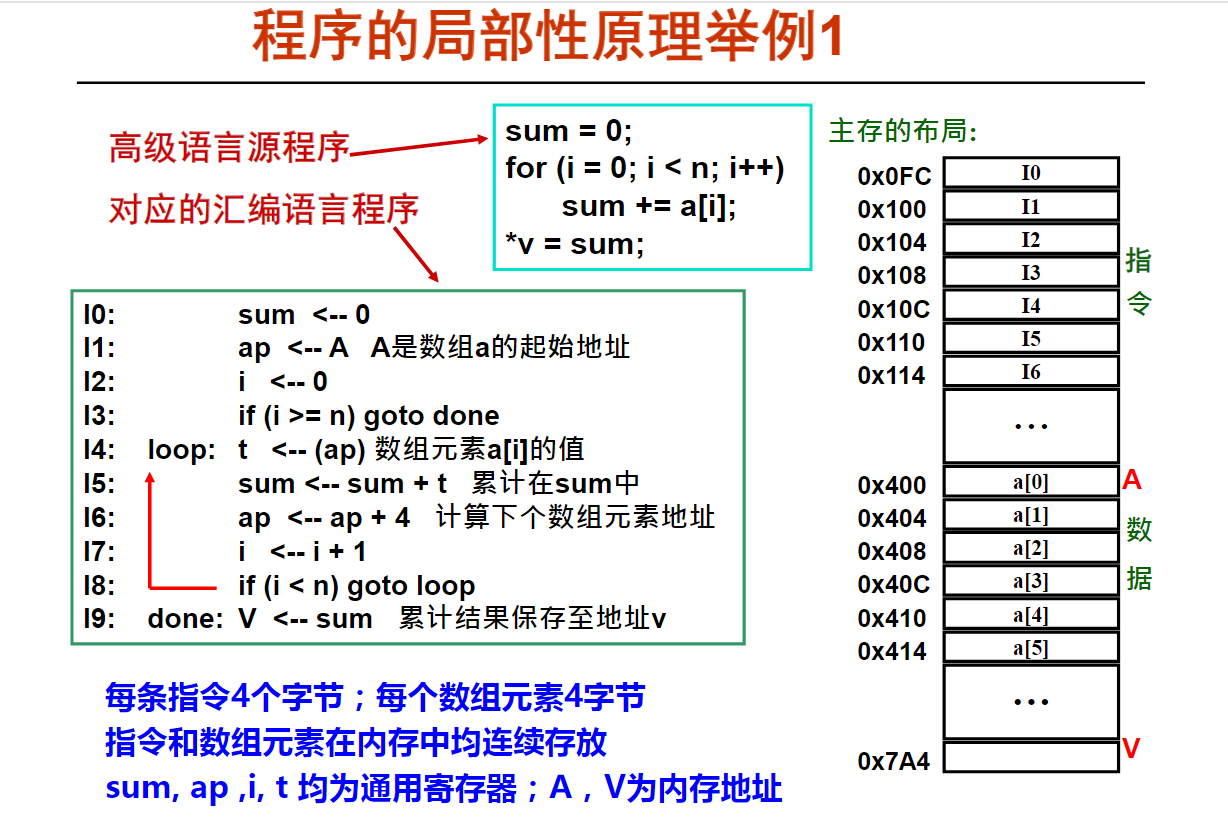

第1讲 存储器层次结构概述(10m44s)

第2讲 Cache基本概述

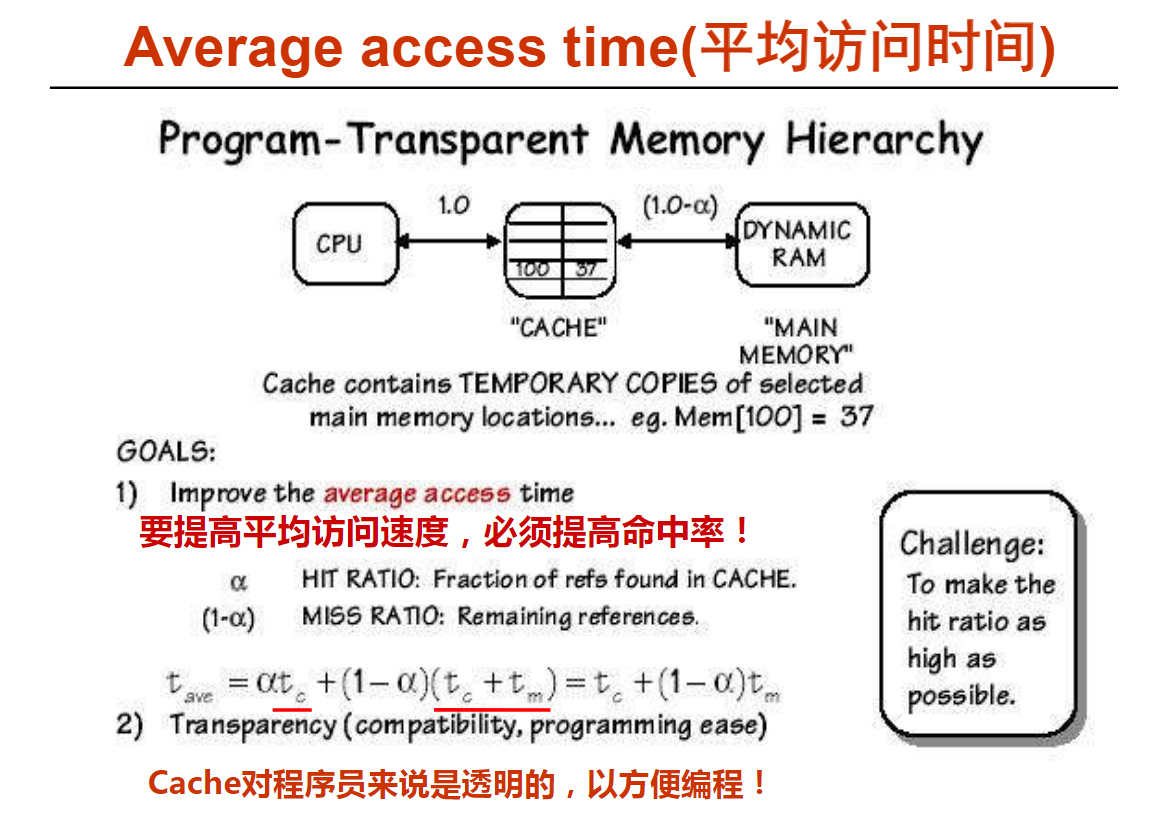

引入Cache的出发点(7m46s)

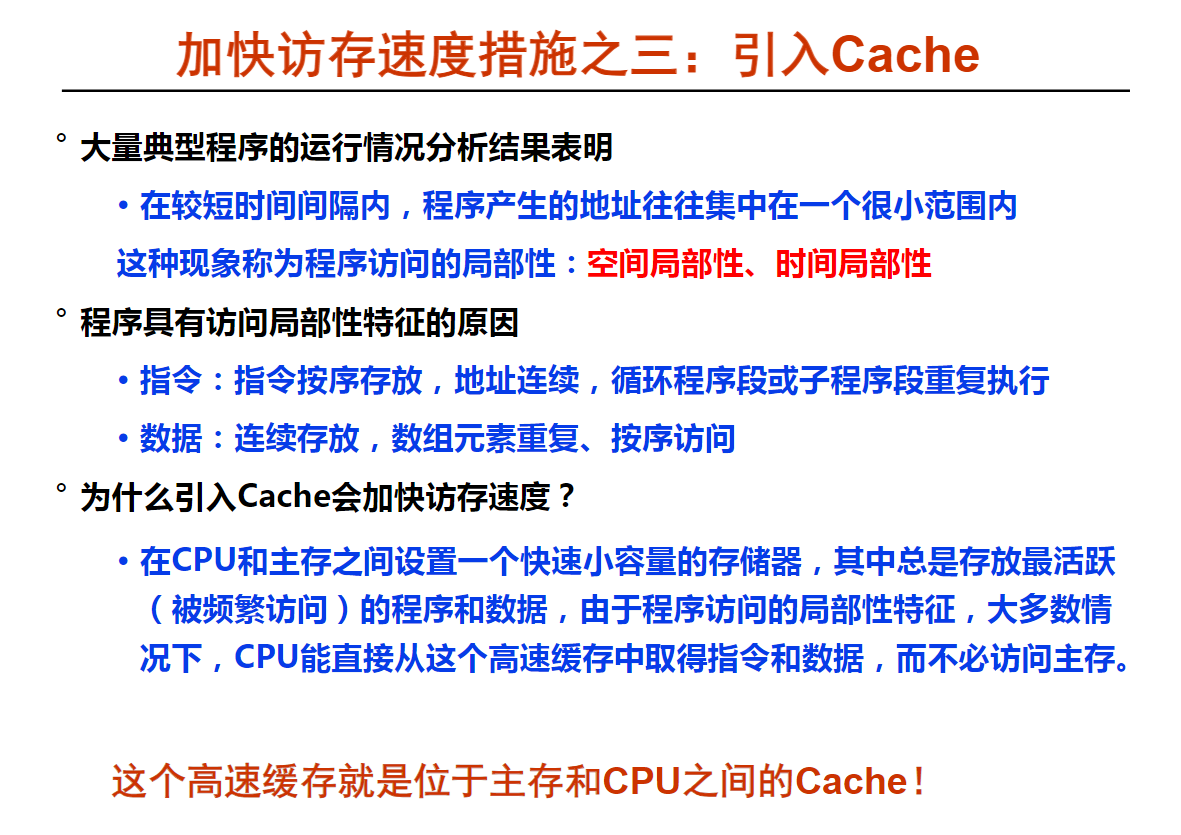

加快访存速度措施之三:引入Cache

怎么获得时钟周期???

程序执行时间

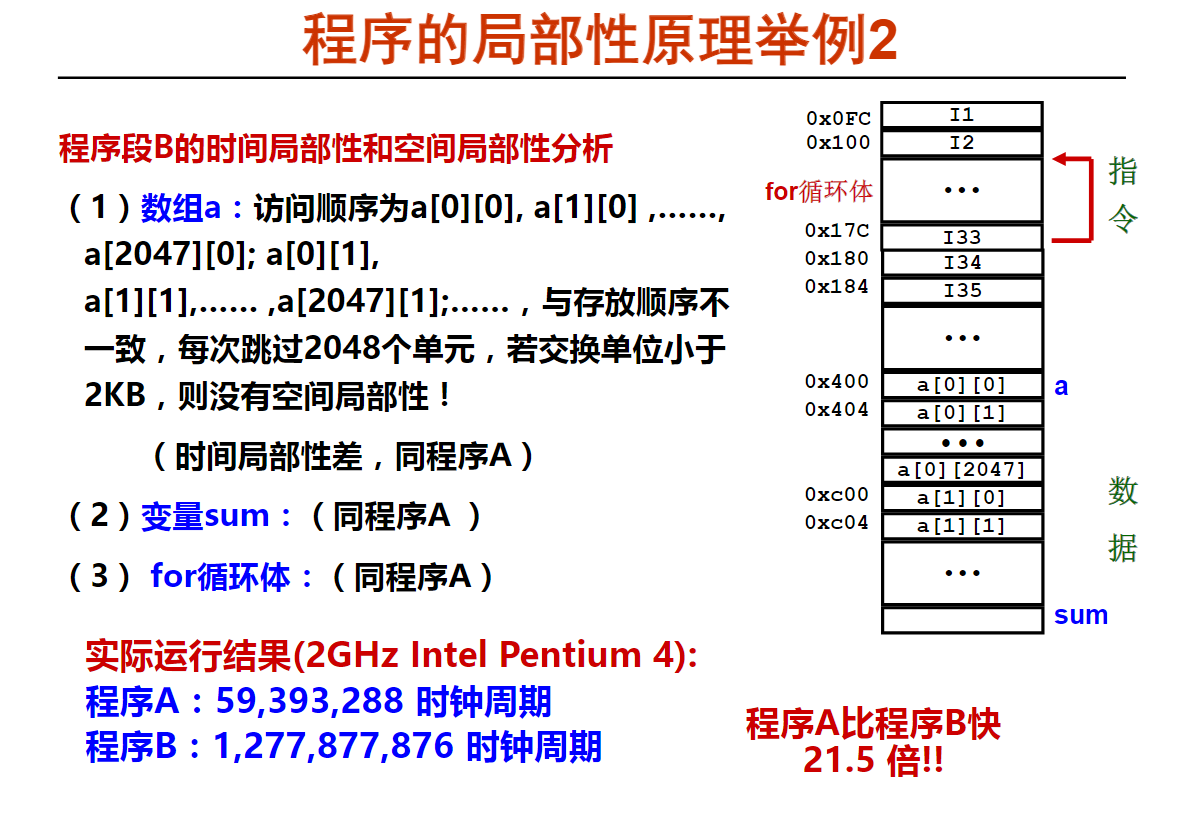

21.5倍

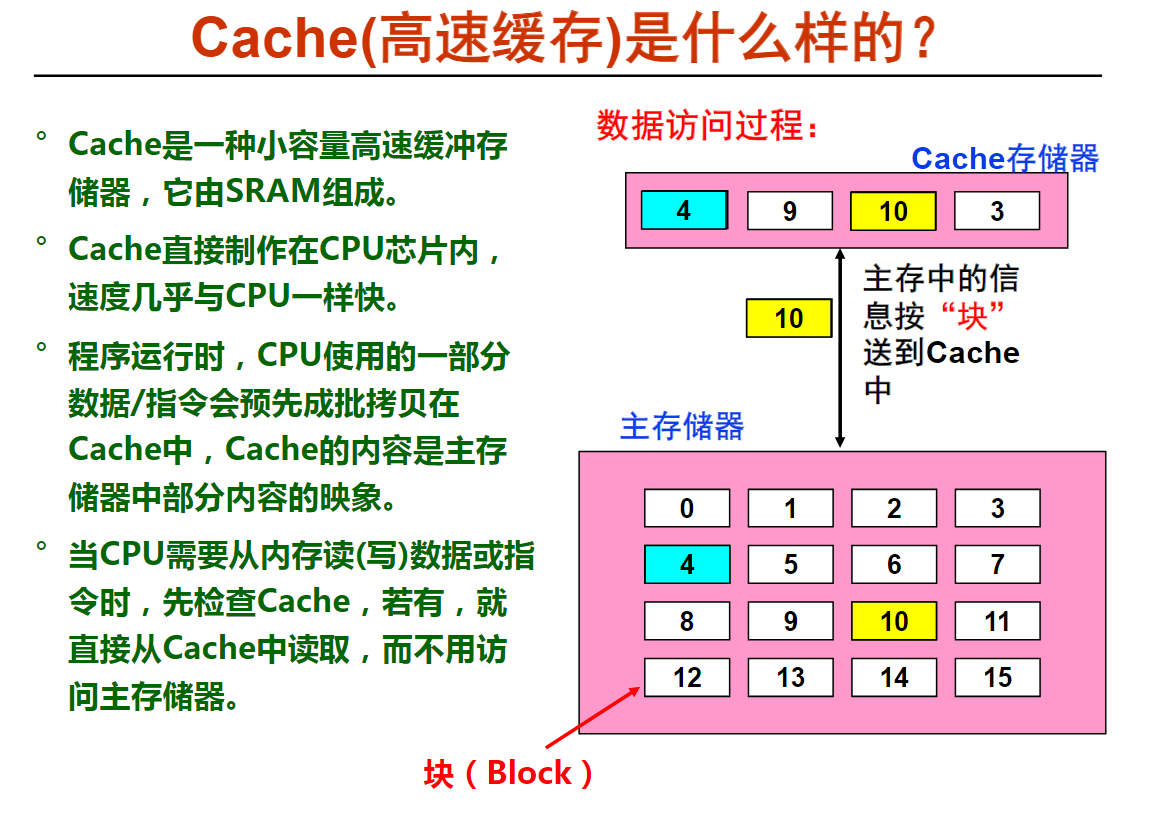

Cache和主存的关系(3m43s)

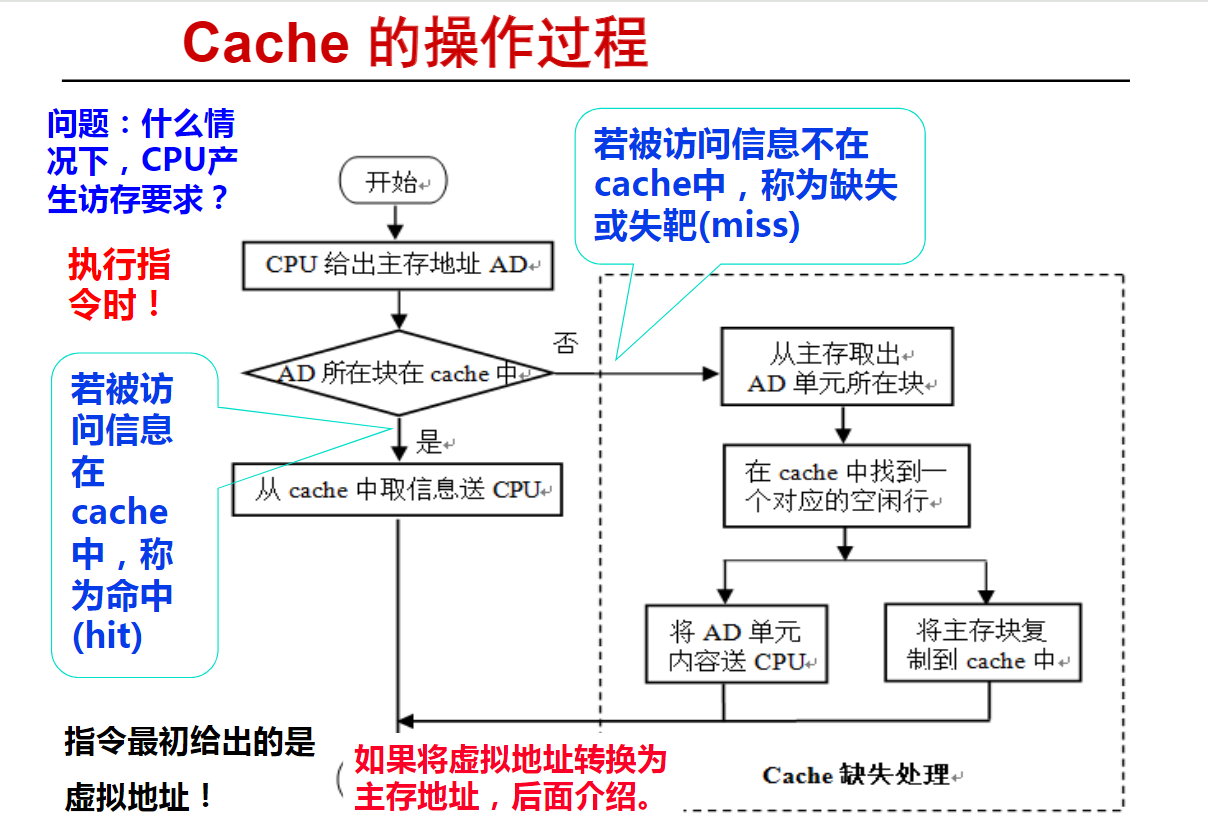

Cache操作过程(4m58s)

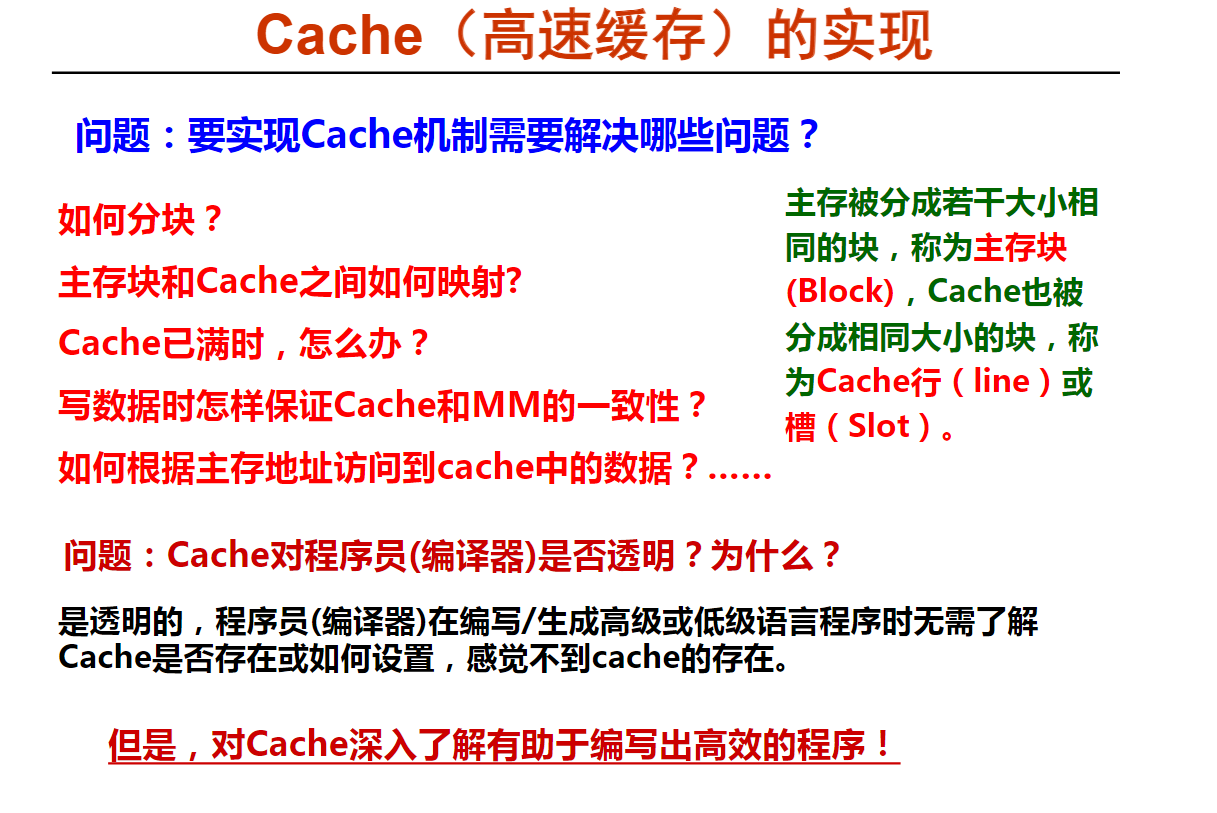

实现Cache需解决的问題(8m06s)

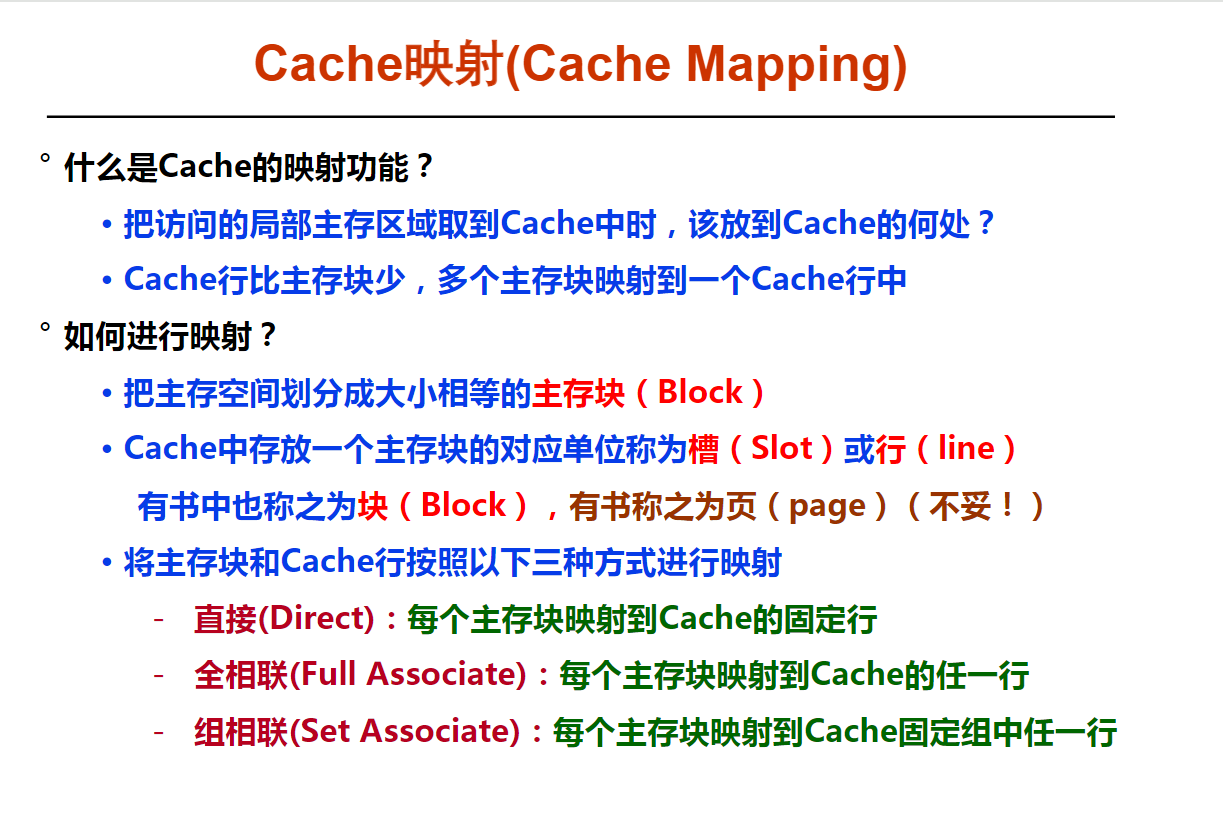

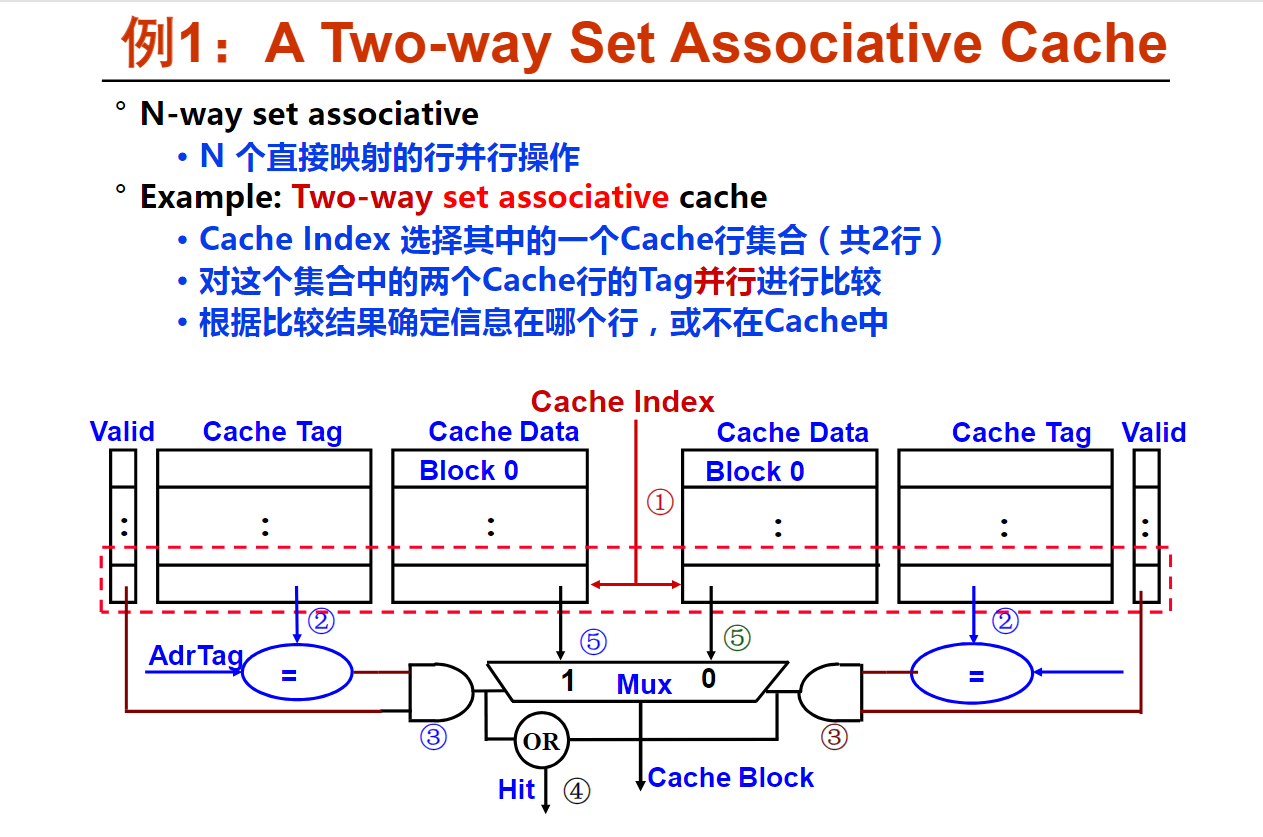

第3讲 Cache映射方式

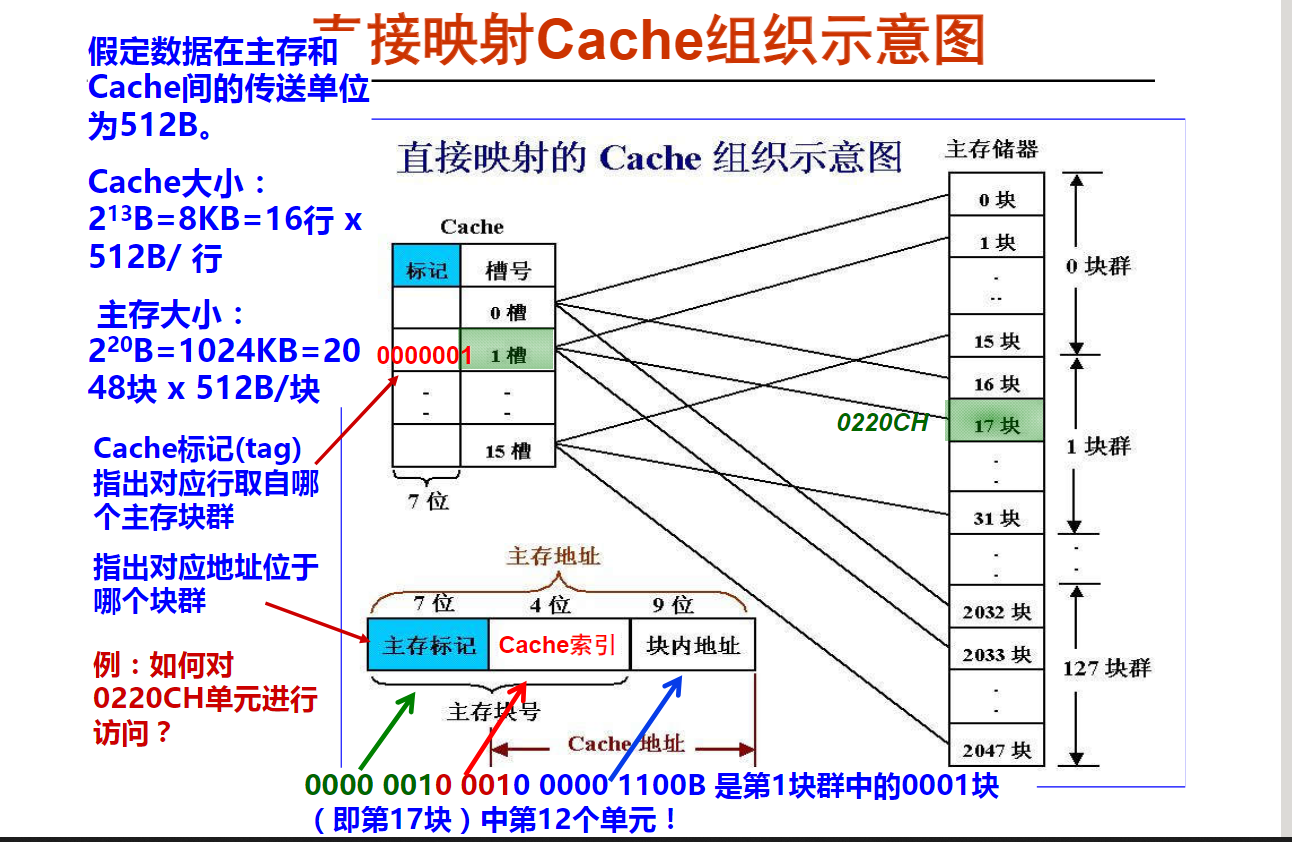

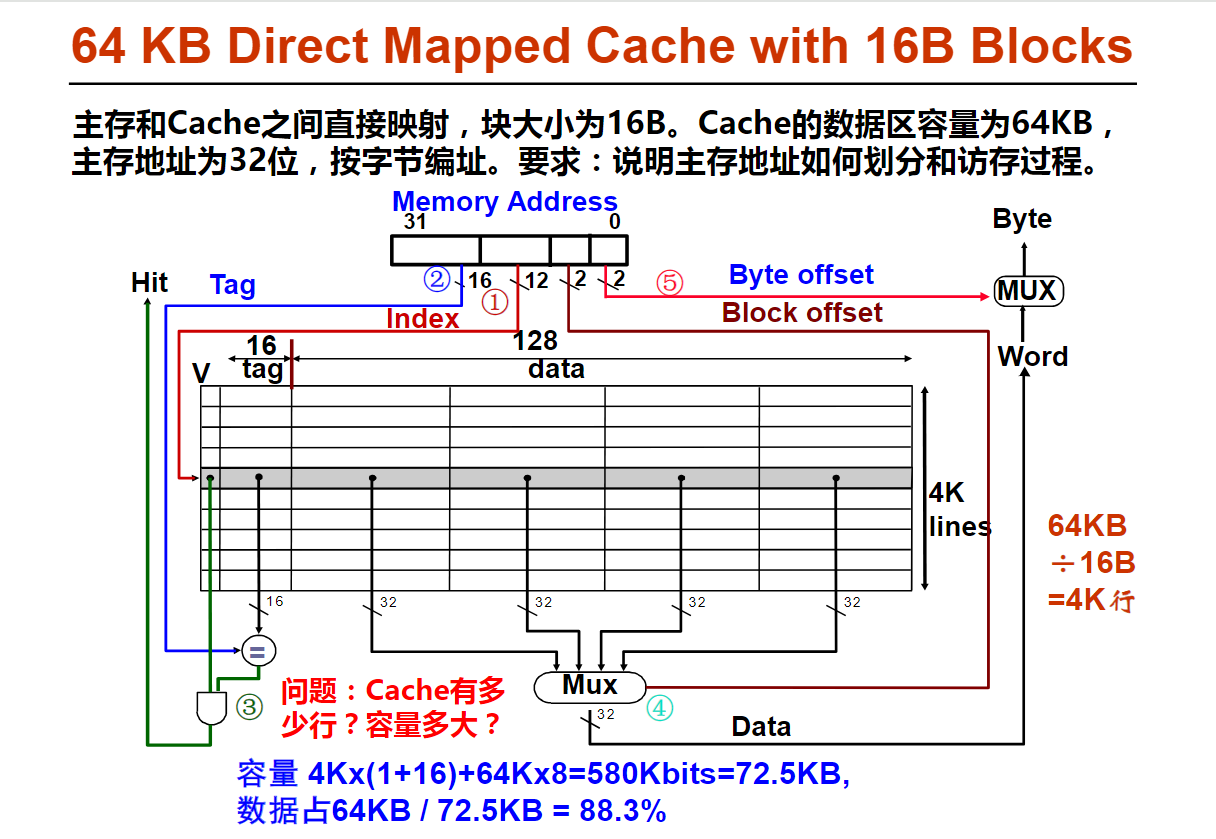

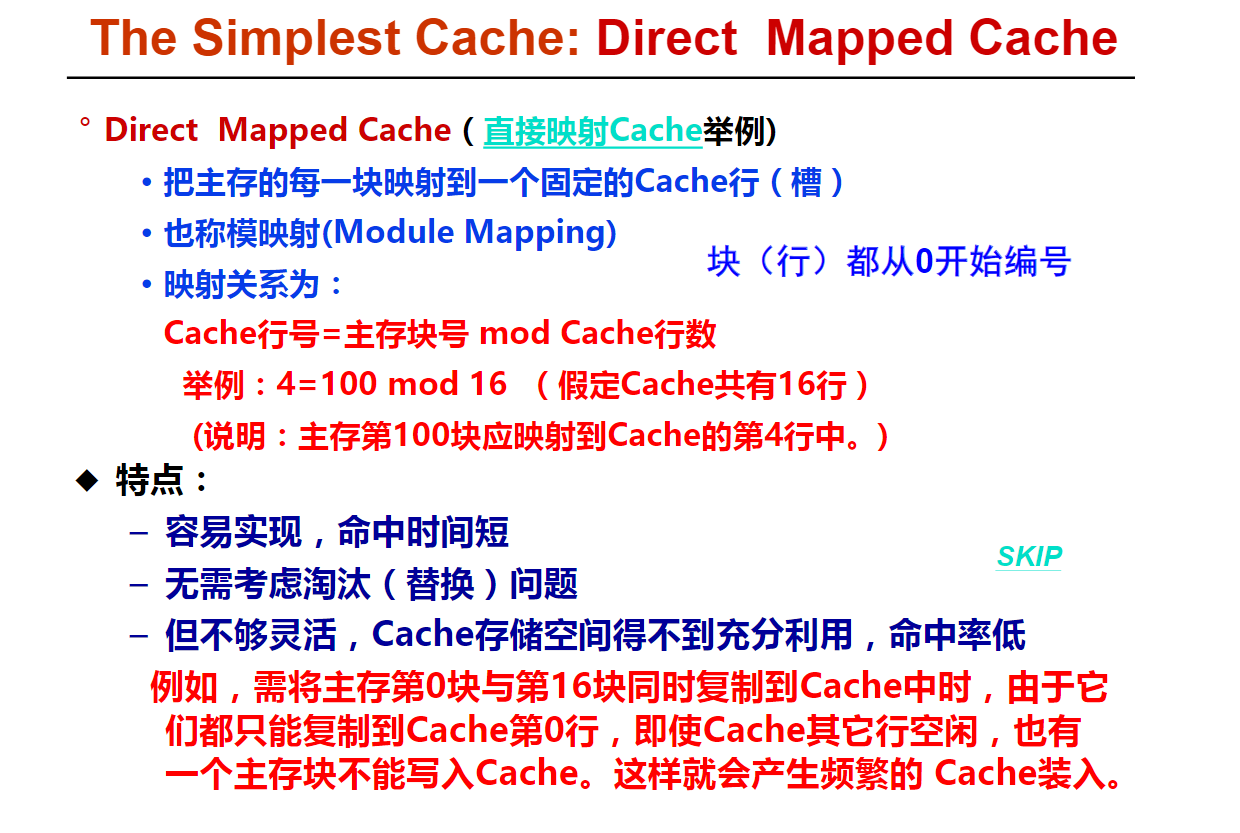

直接映射主存地址划分(14m21s)

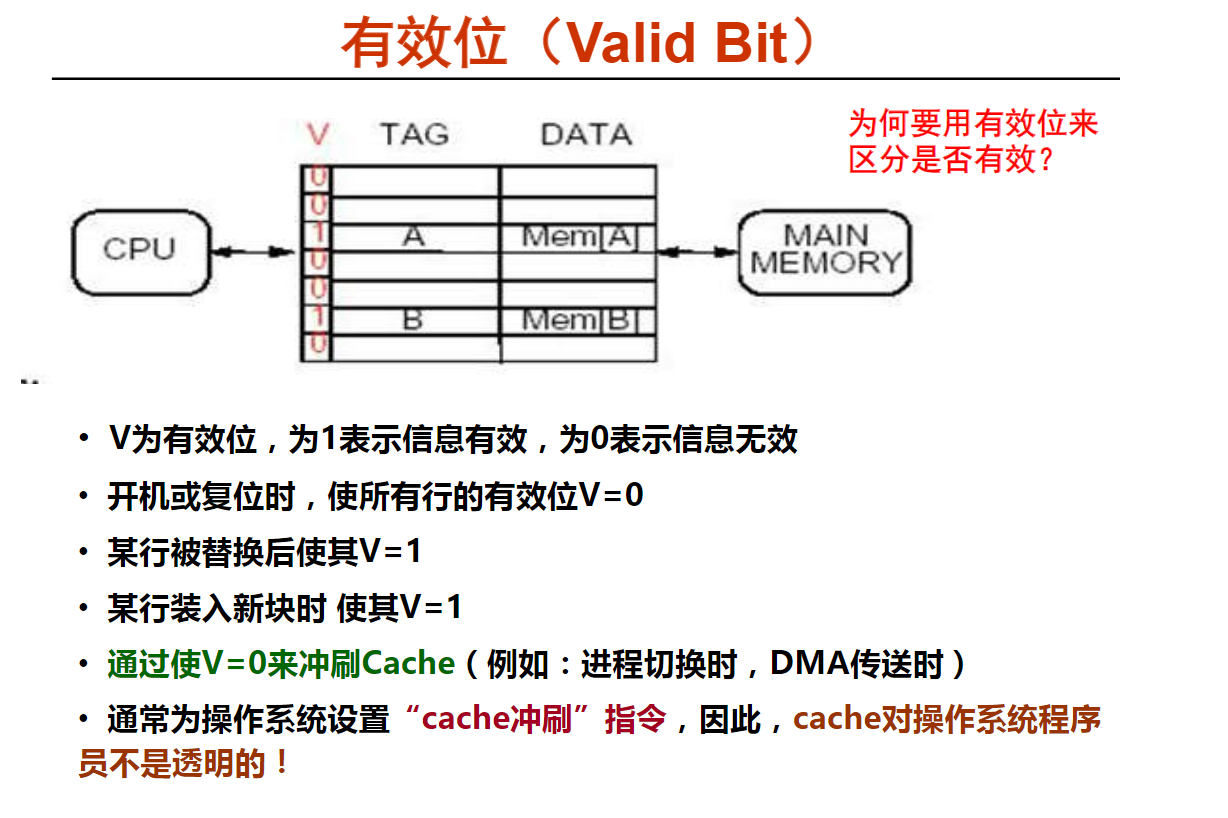

有效位和访存过程(8m59s)

Cache用硬件实现(至多一条指令)

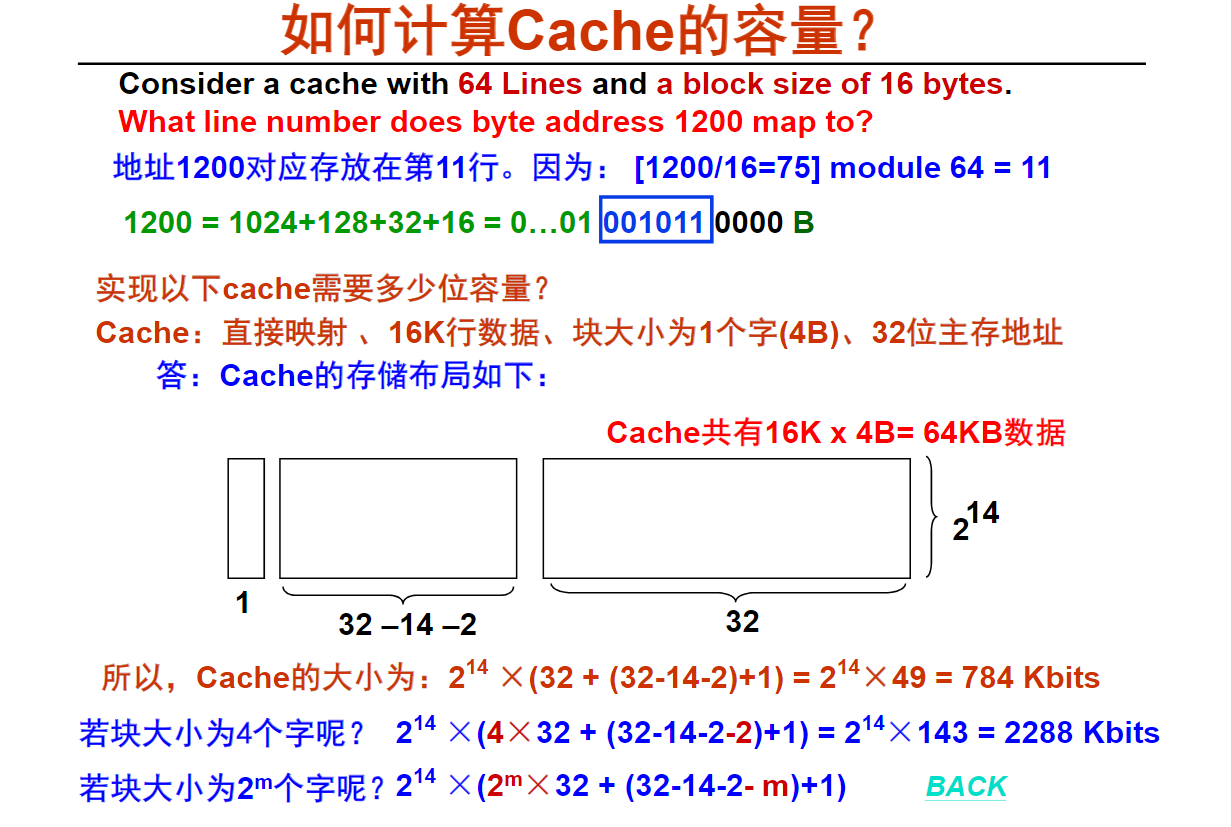

Cache容量的计算(4m48s)

直接映射方式的特点(3m06s)

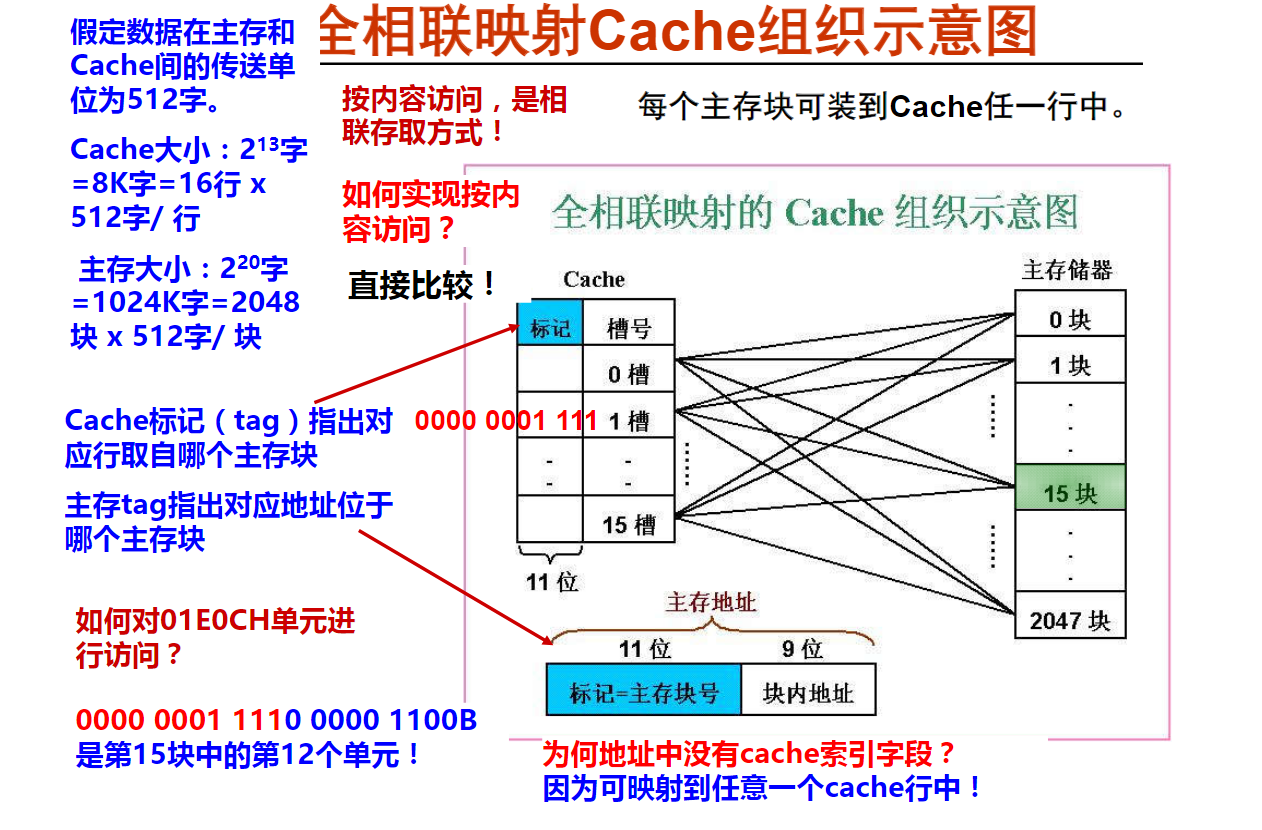

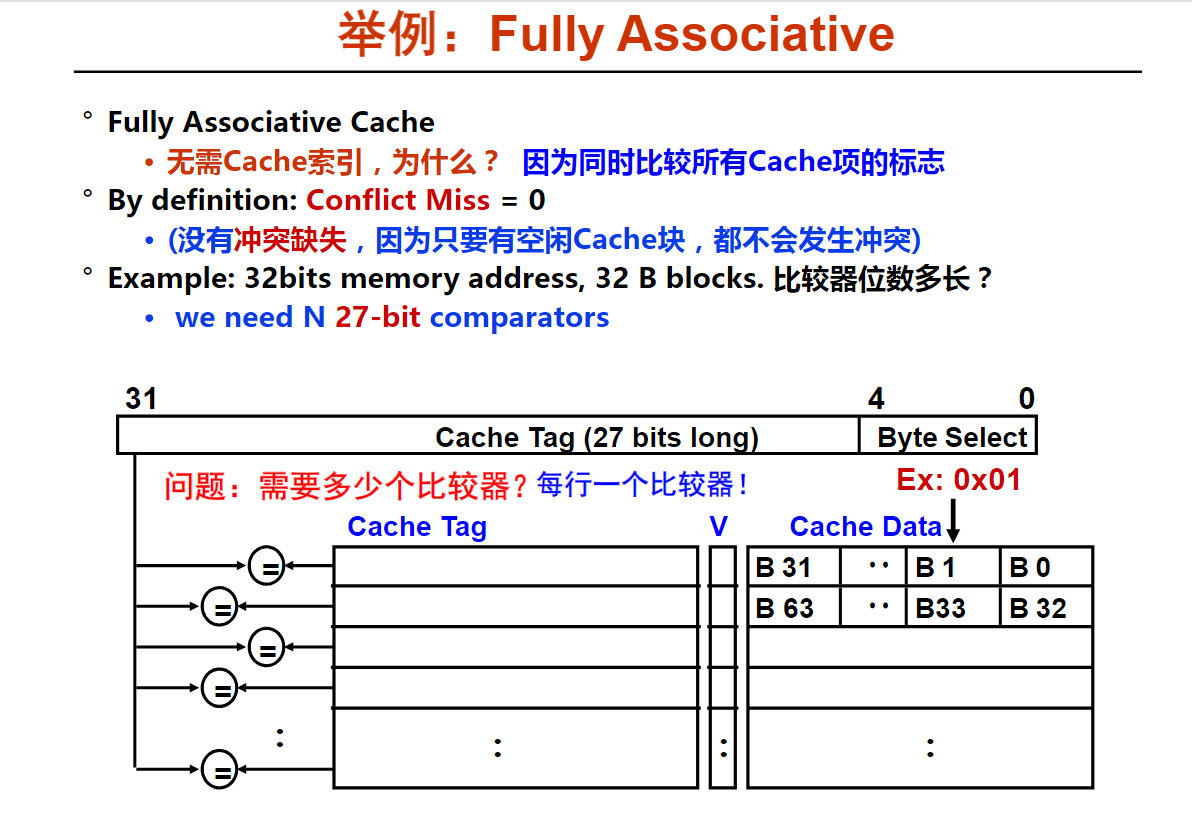

全相联映射方式(5m35s)

这里的字应为字节。

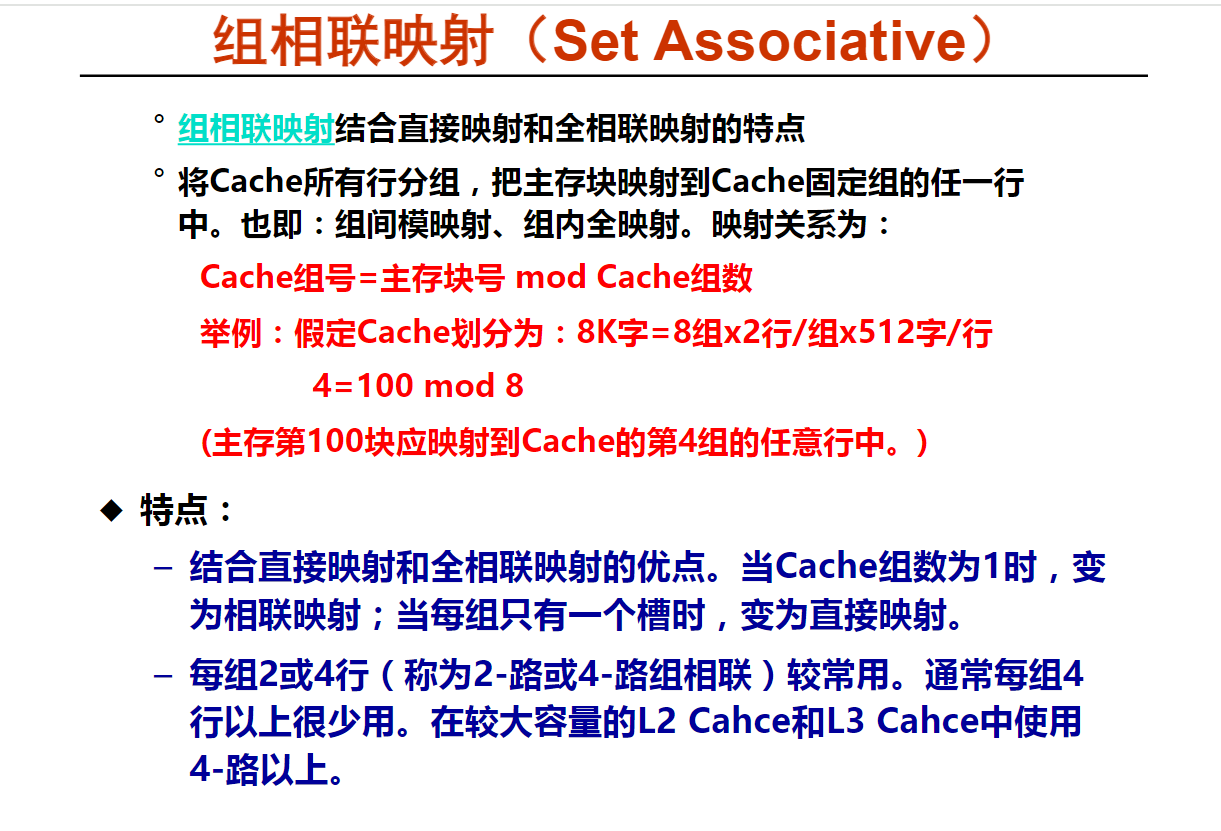

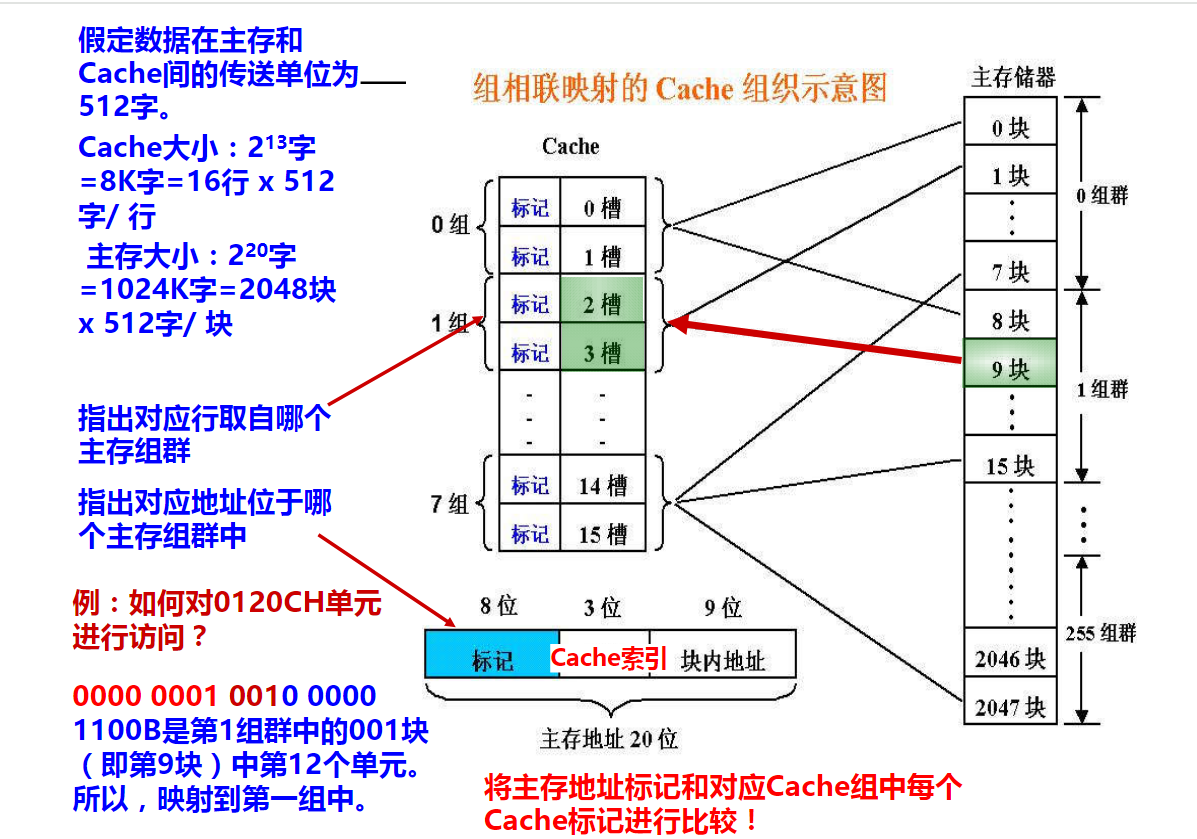

组相联映射方式(7m14s)

这里的字应为字节。

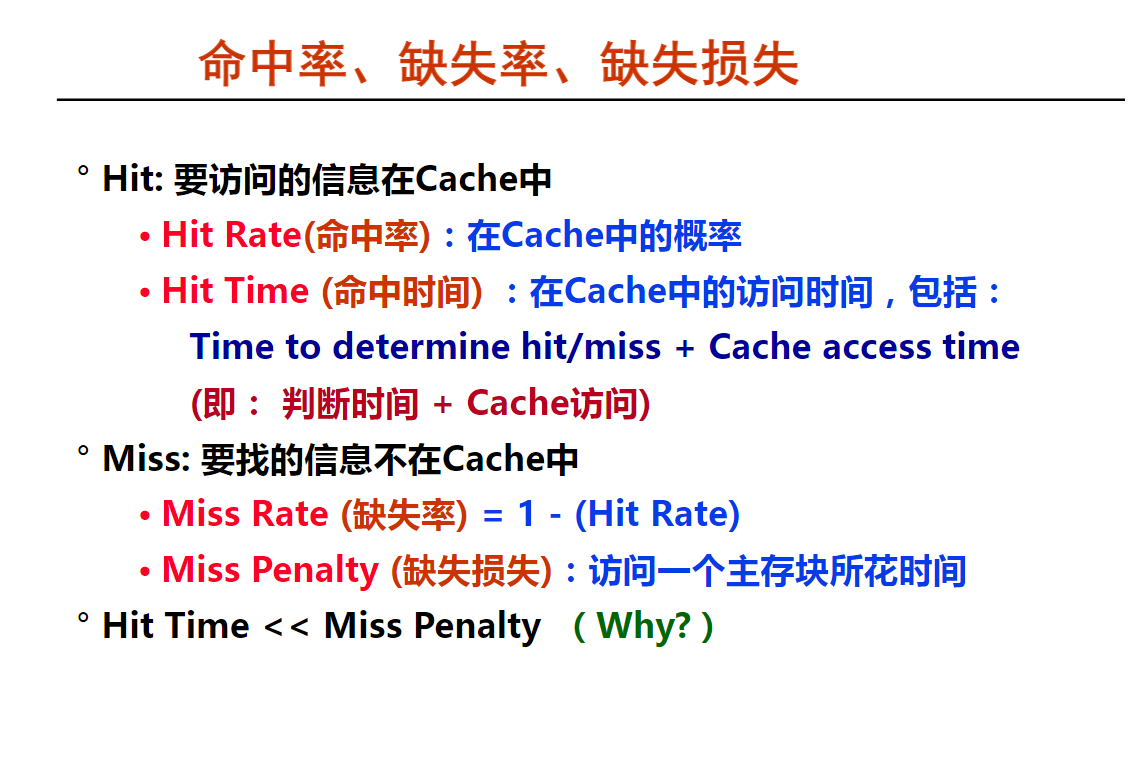

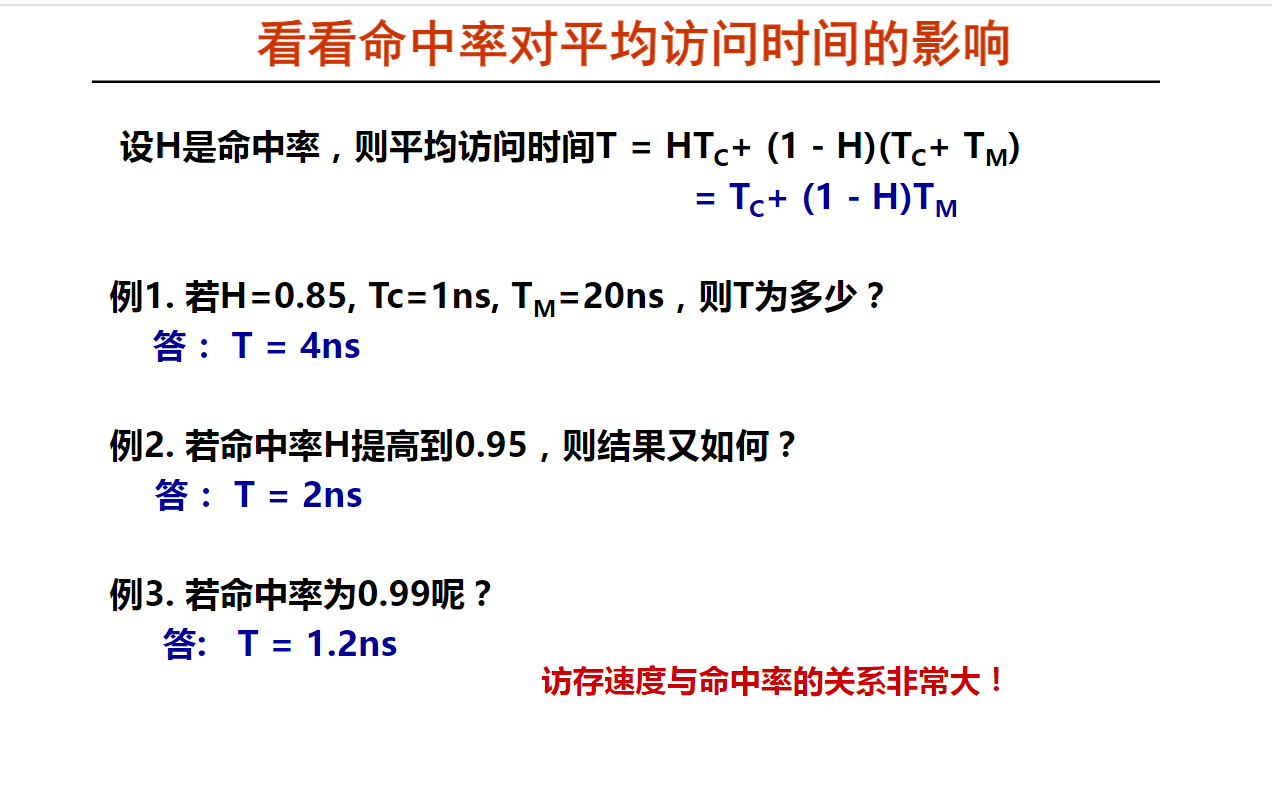

第4讲 Cache命中率和缺失率(5m31s)

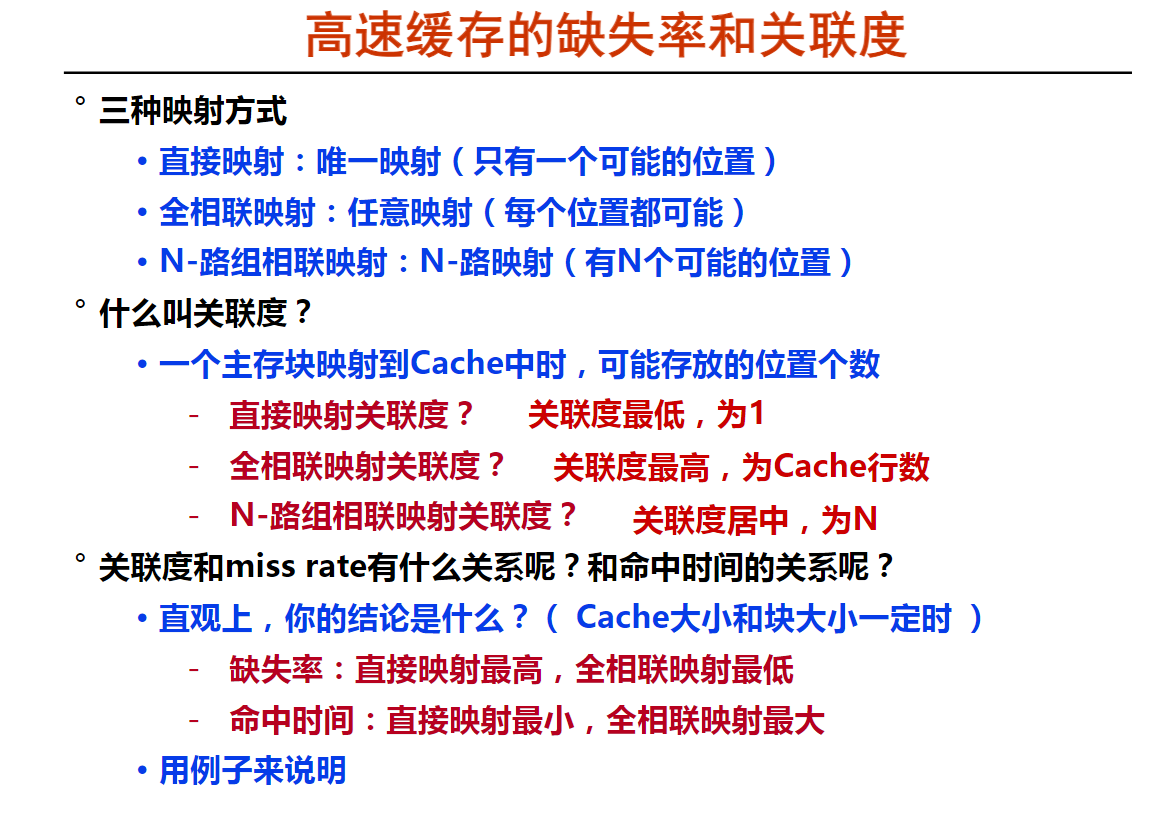

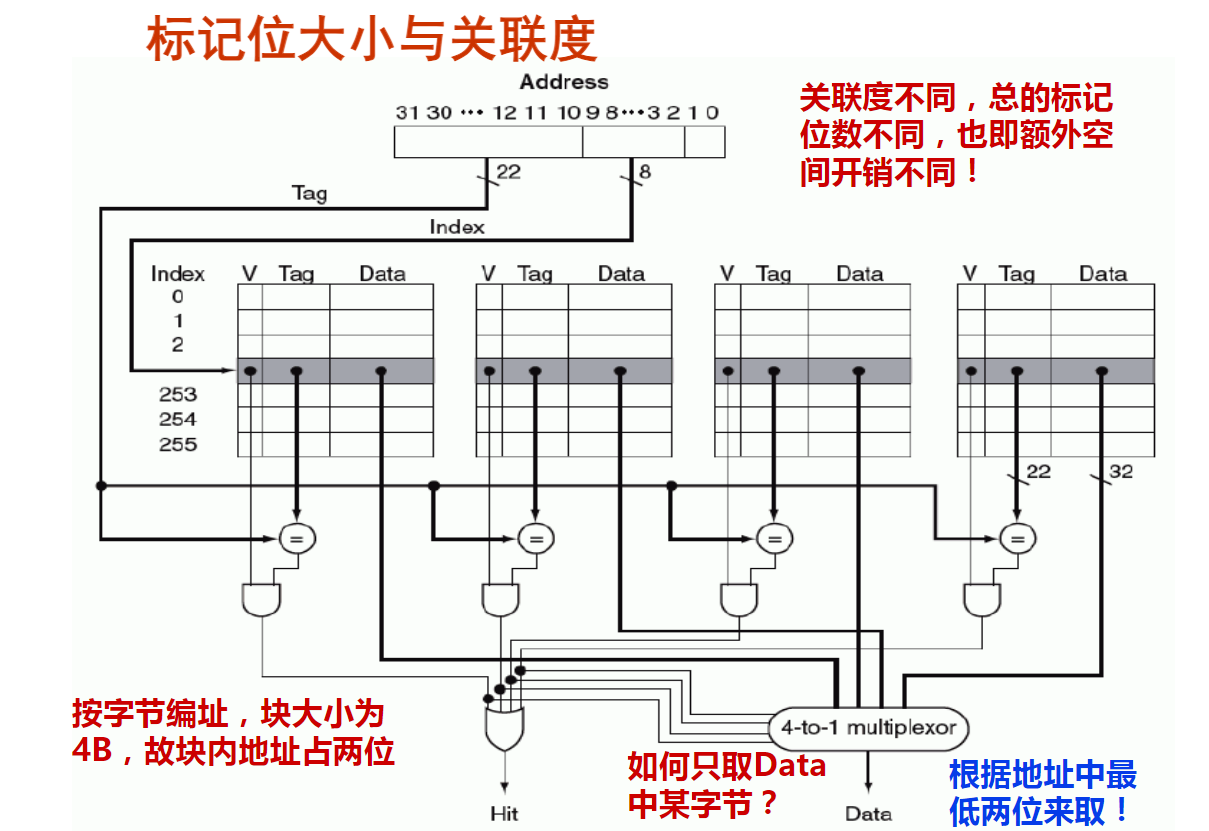

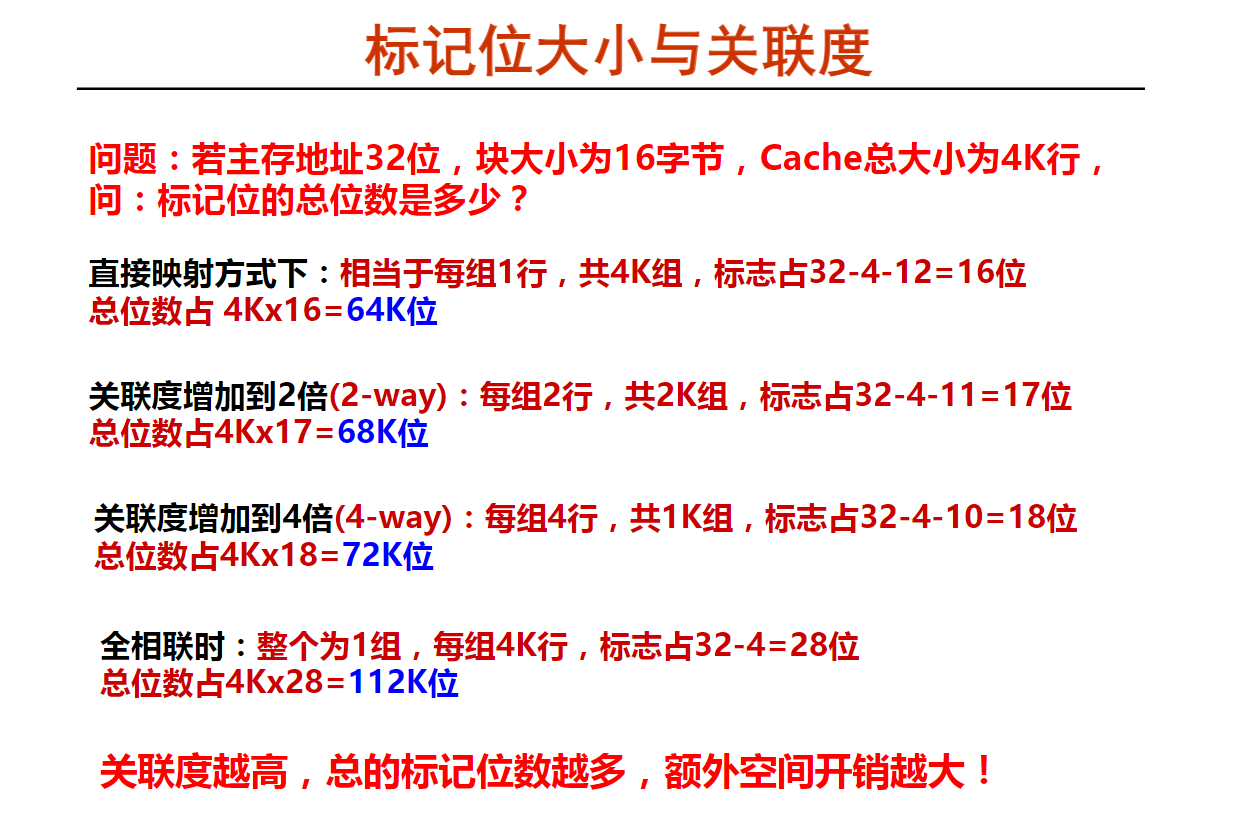

第5讲 Cache的关联度

第四周小测验

1在存储器分层体系结构中,存储器速度从最快到最慢的排列顺序是( C )。

A.寄存器-主存-辅存-cache

B.寄存器-主存-cache-辅存

C.寄存器-cache-主存-辅存

D.寄存器-cache-辅存-主存

正确答案:C你选对了

2在存储器分层体系结构中,存储器从容量最大到最小的排列顺序是(C )。

A.辅存-主存-寄存器-cache

B.主存-辅存-cache-寄存器

C.辅存-主存-cache-寄存器

D.辅存-cache-主存-寄存器

正确答案:C你选对了

3在主存和CPU之间增加cache的目的是( B )。

A.提高内存可靠性

B.加快信息访问速度

C.增加内存容量,同时加快访问速度

D.增加内存容量

正确答案:B你选对了

4以下哪一种情况能很好地发挥cache的作用?

A.程序中含有较多的I/O操作

B.程序的大小不超过实际的内存容量

C.程序具有较好的访问局部性

D.程序的指令间相关度不高

正确答案:C你选对了

5假定主存按字节编址,cache共有64行,采用直接映射方式,主存块大小为32字节,所有编号都从0开始。问主存第2593号单元所在主存块对应的cache行号是( D )。

A.81

B.1

C.34

D.17

解析: D、因为按字节编址,主存块大小为32字节,所以块内地址占5位。采用直接映射方式,共64行,故行号占6位。因为2593=2048+512+32+1=0…01 010001 00001B,根据主存地址划分的结果,可以看出2593单元所在主存块对应的cache行号为010001B=17。

6假定主存按字节编址,cache共有64行,采用4路组相联映射方式,主存块大小为32字节,所有编号都从0开始。问主存第2593号单元所在主存块对应的cache组号是( C )。

A.34

B.81

C.1

D.17

解析: C、因为按字节编址,主存块大小为32字节,所以块内地址占5位。采用4路组相联映射方式,共64行,分64/4=16组,故组号占4位。因为2593=2048+512+32+1=0…0101 0001 00001B,根据主存地址划分的结果,可以看出2593单元所在主存块对应的cache组号为0001B=1。

7假定主存地址空间为256MB,按字节编址, cache共有64行,采用8路组相联映射方式,主存块大小为64B,则cache容量至少为( D )字节。

A.4248

B.4216

C.4224

D.4256

解析: D、因为按字节编址,256M=2^28,故主存地址位数为28位。采用8路组相联,共64行,分64/8=8组,故组号占3位。主存块大小为64B,块内地址占6位。因此,标志位占28-3-6=19位。Cache总容量为64×(1+19+64×8)位=4256字节。

8假定CPU通过存储器总线读取数据的过程为:发送地址和读命令需1个时钟周期,存储器准备一个数据需8个时钟周期,总线上每传送1个数据需1个时钟周期。若主存和cache之间交换的主存块大小为64B,存取宽度和总线宽度都为4B,则cache的一次缺失损失至少为多少个时钟周期?D

A.64

B.80

C.72

D.160

解析: D、一次缺失损失需要从主存读出一个主存块(64B),每个总线事务读取4B,因此,需要64B/4B=16个总线事务。每个总线事务所用时间为1+8+1=10个时钟周期,总共需要160个时钟周期。

9假定用作cache的SRAM的存取时间为2ns,用作主存的SDRAM存储器的存取时间为40ns。为使平均存取时间达到3ns,则cache命中率应为(C )左右。

A.85%

B.99.9%

C.97.5%

D.92.5%

解析: C、1-(3-2)/40=97.5%。

10若主存地址32位,按字节编址,块大小为32字节,cache共有2K行,则以下叙述中,错误的是(D )。

A.关联度为8时,标志位共计38K位

B.关联度为2时,标志位共计34K位

C.关联度为1时,标志位共计32K位

D.全相联时,标志位共计64K位

解析: D、全相联时,标志位共计2K×(32-5)=54K位。